RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 231 of 765

Mar 7, 2023

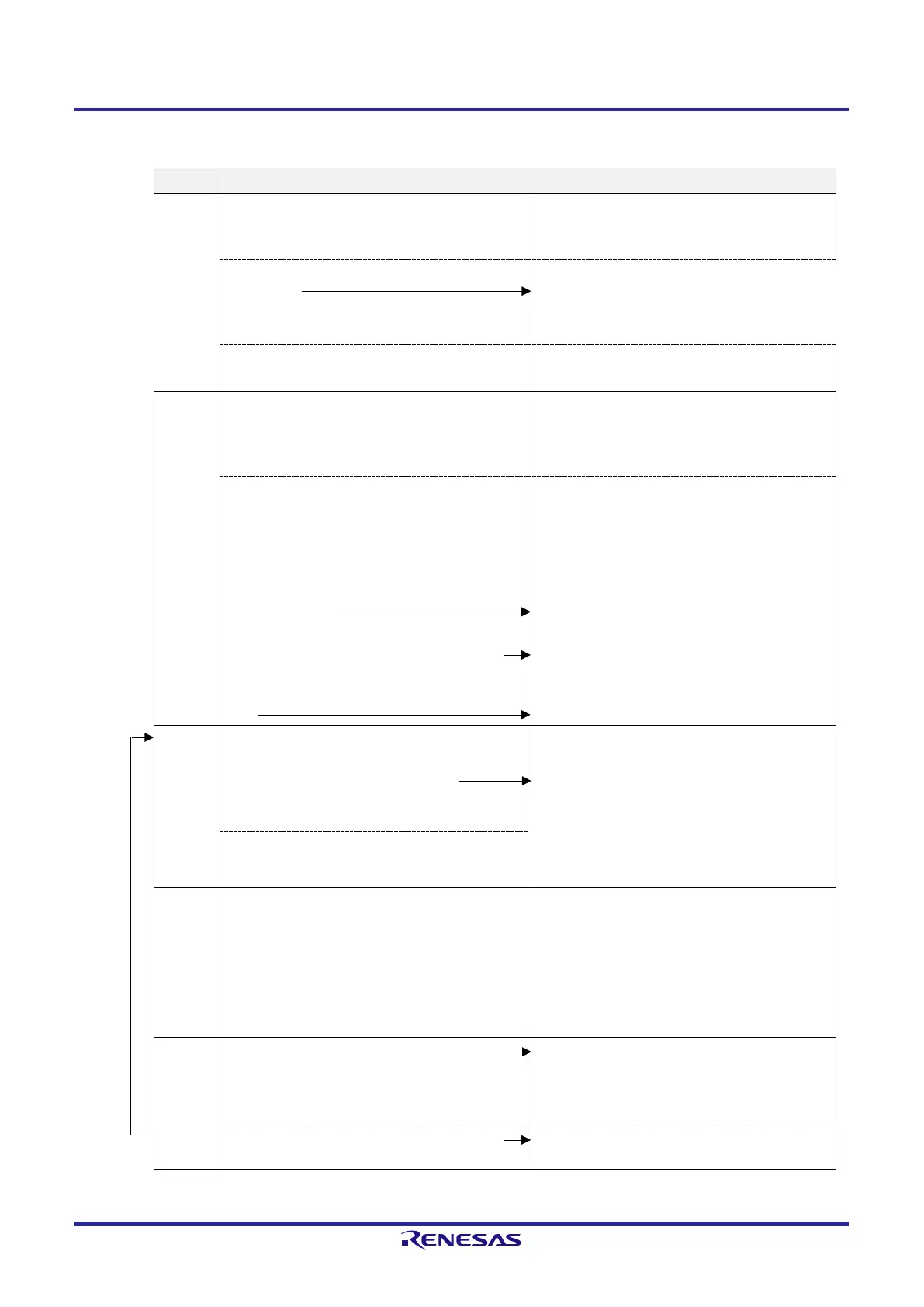

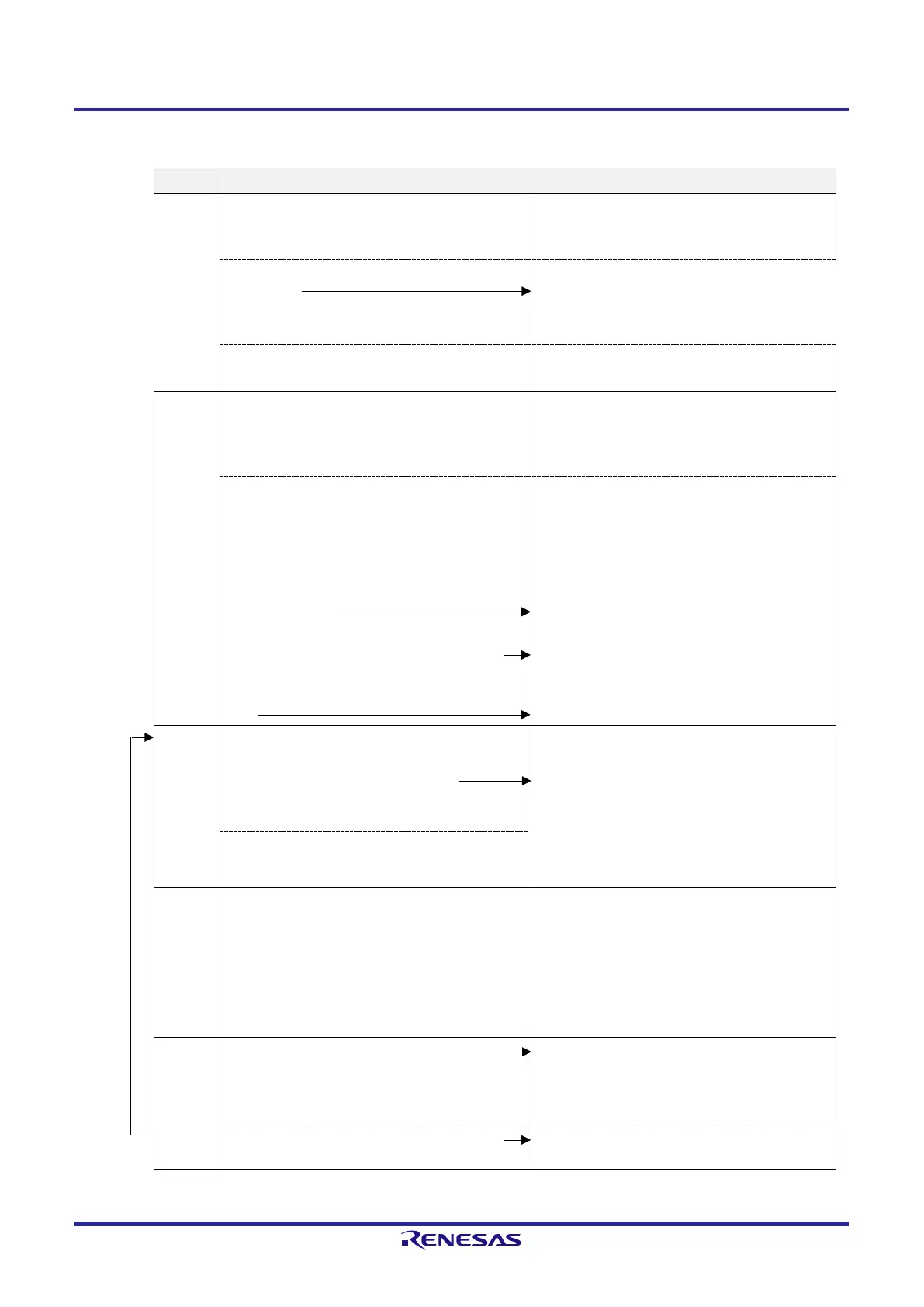

Figure 6-43. Operation Procedure of Interval Timer/Square Wave Output Function (1/2)

Software Operation Hardware Status

TAU

default

setting

Power-off status

(Clock supply is stopped and writing to each register

is disabled.)

Sets the TAUmEN bit of peripheral enable register 0

(PER0) to 1.

Power-on status. Each channel stops operating.

(Clock supply is started and writing to each register is

enabled.)

Sets timer clock select register m (TPSm).

Determines clock frequencies of CKm0 to CKm3.

Channel

default

setting

Sets timer mode register mn (TMRmn) (determines

operation mode of channel).

Sets interval (period) value to timer data register mn

(TDRmn).

Channel stops operating.

(Clock is supplied and some power is consumed.)

To use the TOmn output

Clears the TOMmn bit of timer output mode

register m (TOMm) to 0 (master channel output

mode).

Clears the TOLmn bit to 0.

Sets the TOmn bit and determines default level of

the TOmn output.

The TOmn pin goes into Hi-Z output state.

The TOmn default setting level is output when the port

mode register is in the output mode and the port

register is 0.

Sets the TOEmn bit to 1 and enables operation of

TOmn.

Clears the port register and port mode register to

0.

TOmn does not change because channel stops

operating.

The TOmn pin outputs the TOmn set level.

Operation is resumed.

Operation

start

(Sets the TOEmn bit to 1 only if using TOmn output

and resuming operation.)

Sets the TSmn (TSHm1, TSHm3) bit to 1.

The TSmn (TSHm1, TSHm3) bit automatically

returns to 0 because it is a trigger bit.

TEmn (TEHm1, TEHm3) = 1, and count operation

starts.

Value of the TDRmn register is loaded to timer

count register mn (TCRmn). INTTMmn is

generated and TOmn performs toggle operation if

the MDmn0 bit of the TMRmn register is 1.

During

operation

Set values of the TMRmn register, TOMmn, and

TOLmn bits cannot be changed.

Set value of the TDRmn register can be changed.

The TCRmn register can always be read.

The TSRmn register is not used.

Set values of the TOm and TOEm registers can be

changed.

Counter (TCRmn) counts down. When count value

reaches 0000H, the value of the TDRmn register is

loaded to the TCRmn register again and the count

operation is continued. By detecting TCRmn = 0000H,

INTTMmn is generated and TOmn performs toggle

operation.

After that, the above operation is repeated.

Operation

stop

The TTmn (TTHm1, TTHm3) bit is set to 1.

The TTmn (TTHm1, TTHm3) bit automatically

returns to 0 because it is a trigger bit.

TEmn (TEHm1, TEHm3), and count operation stops.

The TCRmn register holds count value and stops.

The TOmn output is not initialized but holds

current status.

The TOEmn bit is cleared to 0 and value is set to

the TOmn bit.

The TOmn pin outputs the TOmn bit set level.

(Remark is listed on the next page.)

Loading...

Loading...