RL78/G15 CHAPTER 10 A/D CONVERTER

R01UH0959EJ0110 Rev.1.10 Page 324 of 765

Mar 7, 2023

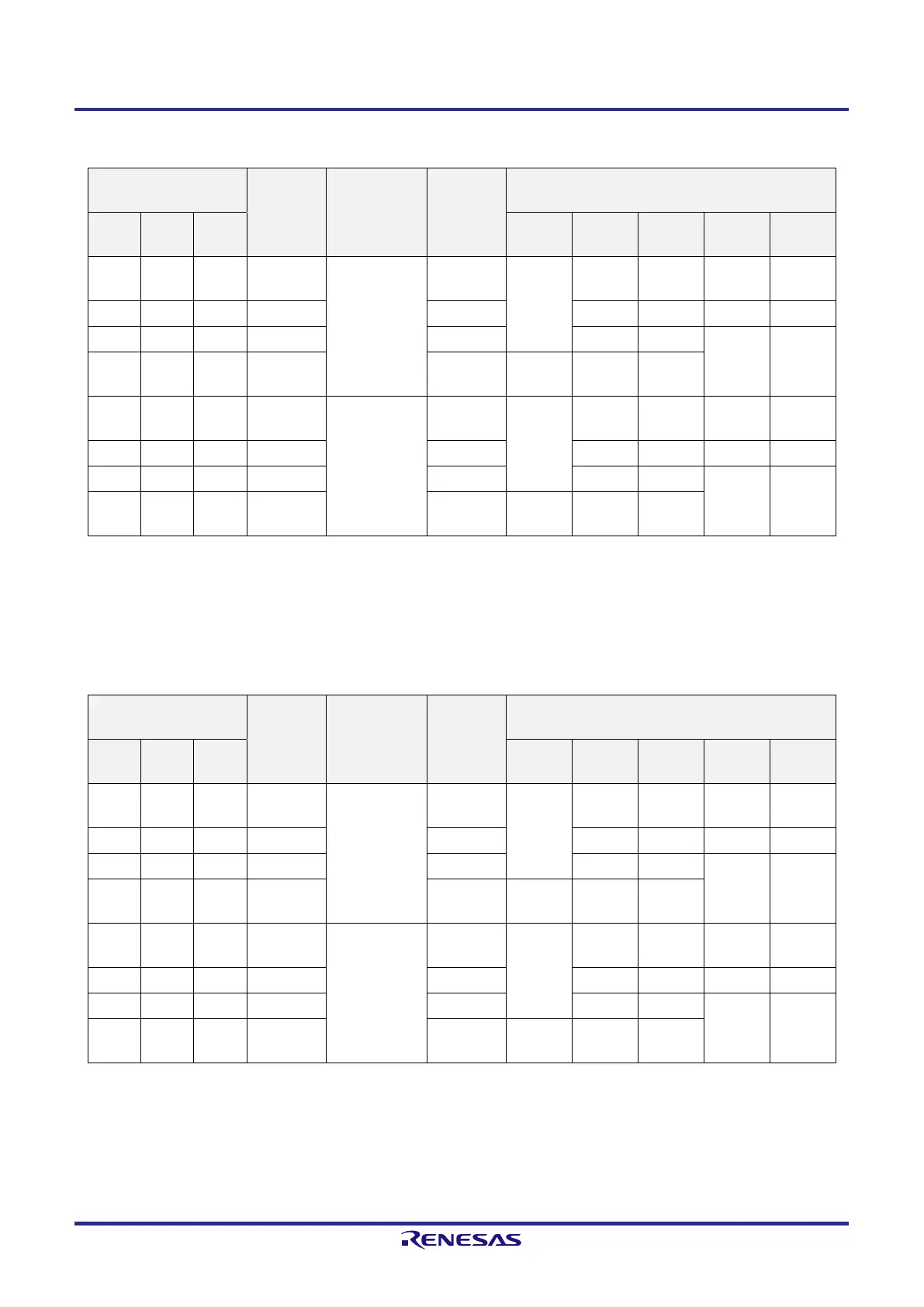

Table 10-2. 10-Bit Resolution A/D Conversion Time Selection

A/D Converter Mode

Register 0 (ADM0)

Conversion

Clock

Number of

Conversion

Clocks

Conversion

Time

Conversion Time Selection (μs)

FR1 FR0

LV0

Note 2

f

CLK

=

1 MHz

f

CLK

=

4 MHz

f

CLK

=

8 MHz

f

CLK

=

10 MHz

f

CLK

=

16 MHz

0 0 0 f

CLK

/8 23 f

AD

(number of

sampling clocks:

9 f

AD

)

184/f

CLK

Setting

prohibited

Setting

prohibited

23.0 18.4 11.5

0 1 f

CLK

/4 92/f

CLK

23.0 11.5 9.2 5.75

1 0 f

CLK

/2 46/f

CLK

11.5 5.75

Setting

prohibited

Setting

prohibited

1 1 f

CLK

23/f

CLK

23.0 5.75

Setting

prohibited

0 0 1

Note 1

f

CLK

/8 17 f

AD

(number of

sampling clocks:

3 f

AD

)

136/f

CLK

Setting

prohibited

Setting

prohibited

17.0 13.6 8.5

0 1 f

CLK

/4 68/f

CLK

17.0 8.5 6.8 4.25

1 0 f

CLK

/2 34/f

CLK

8.5 4.25

Setting

prohibited

Setting

prohibited

1 1 f

CLK

17/f

CLK

17.0 4.25

Setting

prohibited

Note 1. Setting is prohibited when 2.4 V ≤ V

DD

< 2.7 V. Can be selected when 2.7 V ≤ V

DD

≤ 5.5 V.

Note 2. When the internal reference voltage is selected as the target of conversion by the A/D converter, be sure to

clear the LV0 bit to 0.

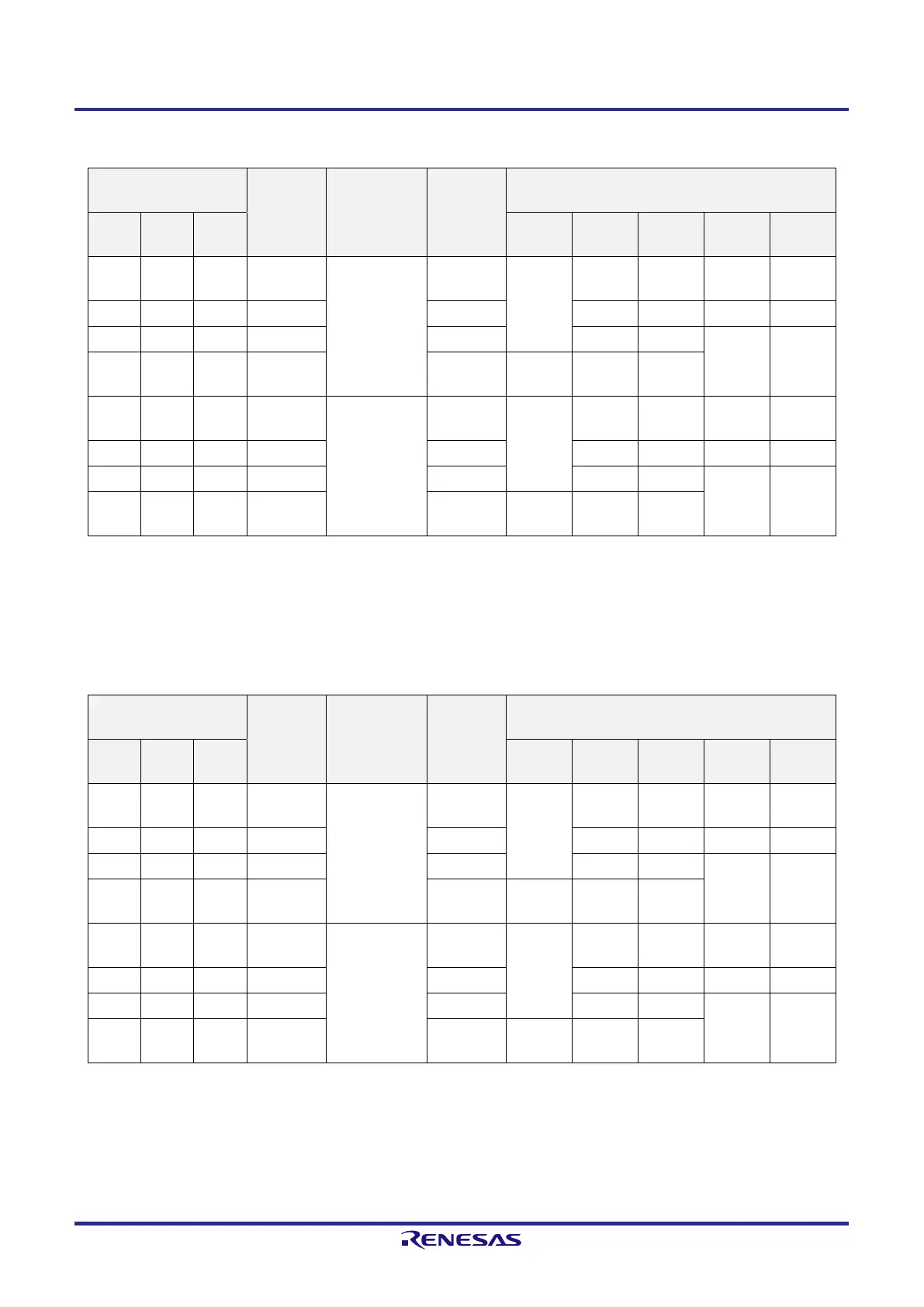

Table 10-3. 8-Bit Resolution A/D Conversion Time Selection

A/D Converter Mode

Register 0 (ADM0)

Conversion

Clock

Number of

Conversion

Clocks

Conversion

Time

Conversion Time Selection (μs)

FR1 FR0

LV0

Note 2

f

CLK

=

1 MHz

f

CLK

=

4 MHz

f

CLK

=

8 MHz

f

CLK

=

10 MHz

f

CLK

=

16 MHz

0 0 0 f

CLK

/8 21 f

AD

(number of

sampling clocks:

9 f

AD

)

168/f

CLK

Setting

prohibited

Setting

prohibited

21.0 16.8 10.5

0 1 f

CLK

/4 84/f

CLK

21.0 10.5 8.4 5.25

1 0 f

CLK

/2 42/f

CLK

10.5 5.25

Setting

prohibited

Setting

prohibited

1 1 f

CLK

21/f

CLK

21.0 5.25

Setting

prohibited

0 0 1

Note 1

f

CLK

/8 15 f

AD

(number of

sampling clocks:

3 f

AD

)

120/f

CLK

Setting

prohibited

Setting

prohibited

15.0 12.0 7.5

0 1 f

CLK

/4 60/f

CLK

15.0 7.5 6.0 3.75

1 0 f

CLK

/2 30/f

CLK

7.5 3.75

Setting

prohibited

Setting

prohibited

1 1 f

CLK

15/f

CLK

15.0

Setting

prohibited

Setting

prohibited

Note 1. Setting is prohibited when 2.4 V ≤ V

DD

< 2.7 V. Can be selected when 2.7 V ≤ V

DD

≤ 5.5 V.

Note 2. When the internal reference voltage is selected as the target of conversion by the A/D converter, be sure to

clear the LV0 bit to 0.

Caution 1. The A/D conversion time must also be within the range of the conversion time (t

CONV

) indicated in

23.6.1 A/D converter characteristics or 24.6.1 A/D converter characteristics.

Loading...

Loading...