8–46 Chapter 8: Configuration and Remote System Upgrades in Cyclone IV Devices

Configuration

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

JTAG instructions have precedence over any other configuration modes. Therefore,

JTAG configuration can take place without waiting for other configuration modes to

complete. For example, if you attempt JTAG configuration in Cyclone IV devices

during PS configuration, PS configuration terminates and JTAG configuration begins.

If the

MSEL

pins are set to AS mode, the Cyclone IV device does not output a

DCLK

signal when JTAG configuration takes place.

The four required pins for a device operating in JTAG mode are

TDI

,

TDO

,

TMS

, and

TCK

.

All the JTAG input pins are powered by the V

CCIO

pin and support the LVTTL I/O

standard only. All user I/O pins are tri-stated during JTAG configuration. Table 8–14

explains the function of each JTAG pin.

You can download data to the device through the USB-Blaster, MasterBlaster,

ByteBlaster II, or ByteBlasterMV download cable, or the EthernetBlaster

communications cable during JTAG configuration. Configuring devices with a cable is

similar to programming devices in-system. Figure 8–23 and Figure 8–24 show the

JTAG configuration of a single Cyclone IV device.

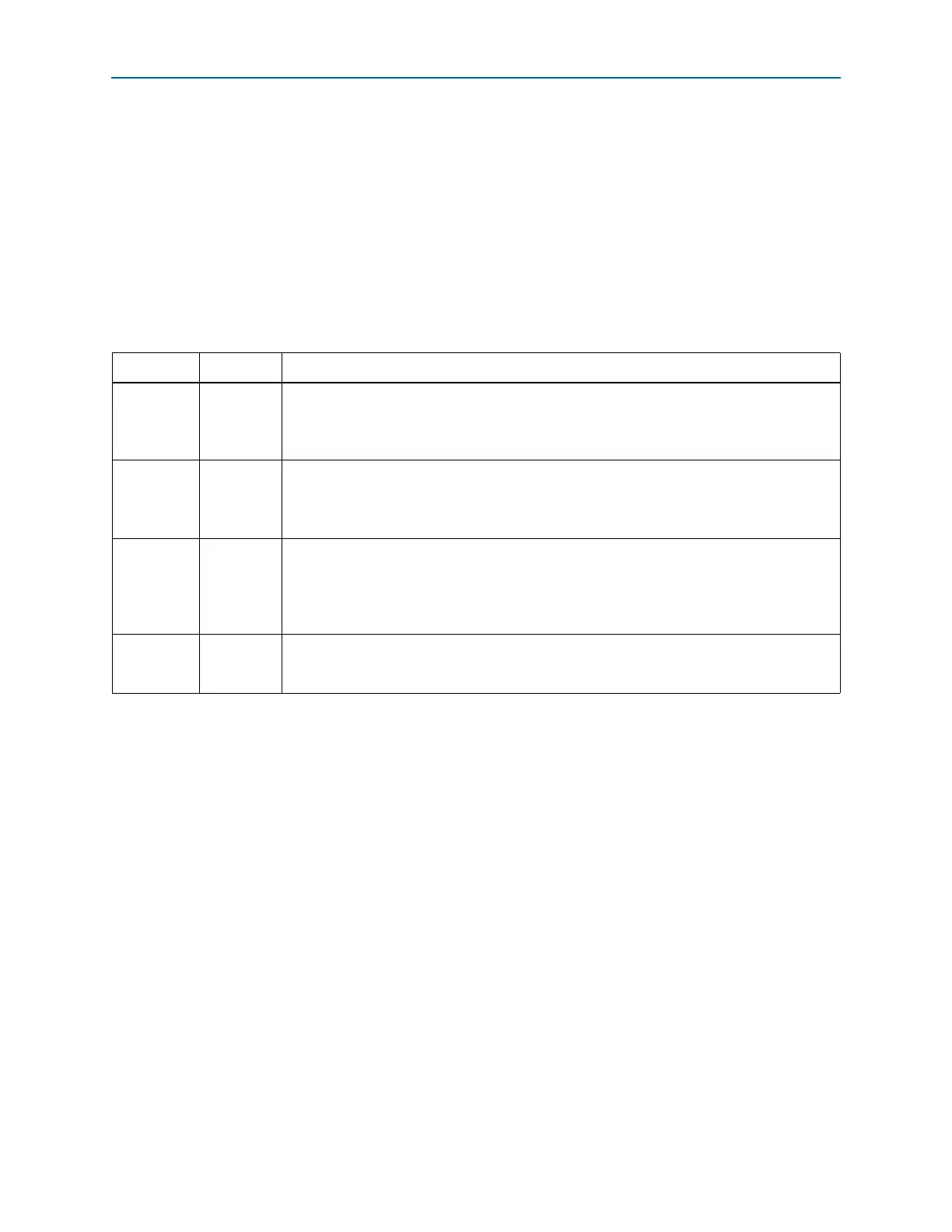

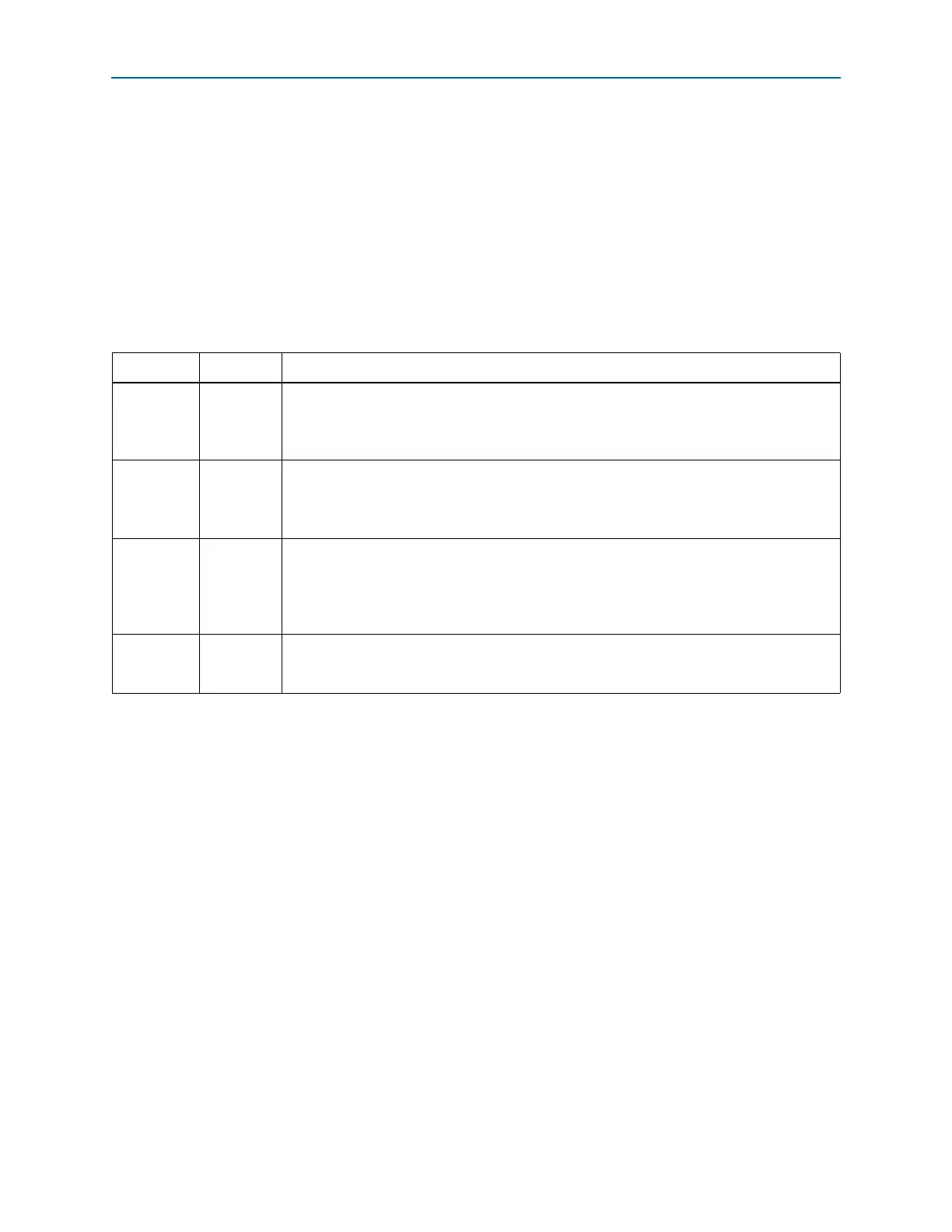

Table 8–14. Dedicated JTAG Pins

Pin Name Pin Type Description

TDI

Test data

input

Serial input pin for instructions as well as test and programming data. Data shifts in on the

rising edge of

TCK

. If the JTAG interface is not required on the board, the JTAG circuitry is

disabled by connecting this pin to V

CC

.

TDI

pin has weak internal pull-up resistors (typically 25

k).

TDO

Test data

output

Serial data output pin for instructions as well as test and programming data. Data shifts out on

the falling edge of

TCK

. The pin is tri-stated if data is not being shifted out of the device. If the

JTAG interface is not required on the board, the JTAG circuitry is disabled by leaving this pin

unconnected.

TMS

Test mode

select

Input pin that provides the control signal to determine the transitions of the TAP controller

state machine. Transitions in the state machine occur on the rising edge of

TCK

. Therefore,

TMS

must be set up before the rising edge of

TCK

.

TMS

is evaluated on the rising edge of

TCK

.

If the JTAG interface is not required on the board, the JTAG circuitry is disabled by connecting

this pin to V

CC

.

TMS

pin has weak internal pull-up resistors (typically 25 k).

TCK

Test clock

input

The clock input to the BST circuitry. Some operations occur at the rising edge, while others

occur at the falling edge. If the JTAG interface is not required on the board, the JTAG circuitry

is disabled by connecting this pin to GND. The

TCK

pin has an internal weak pull-down resistor.

Loading...

Loading...