1–32 Chapter 1: Cyclone IV Transceivers Architecture

Transceiver Clocking Architecture

Cyclone IV Device Handbook, February 2015 Altera Corporation

Volume 2

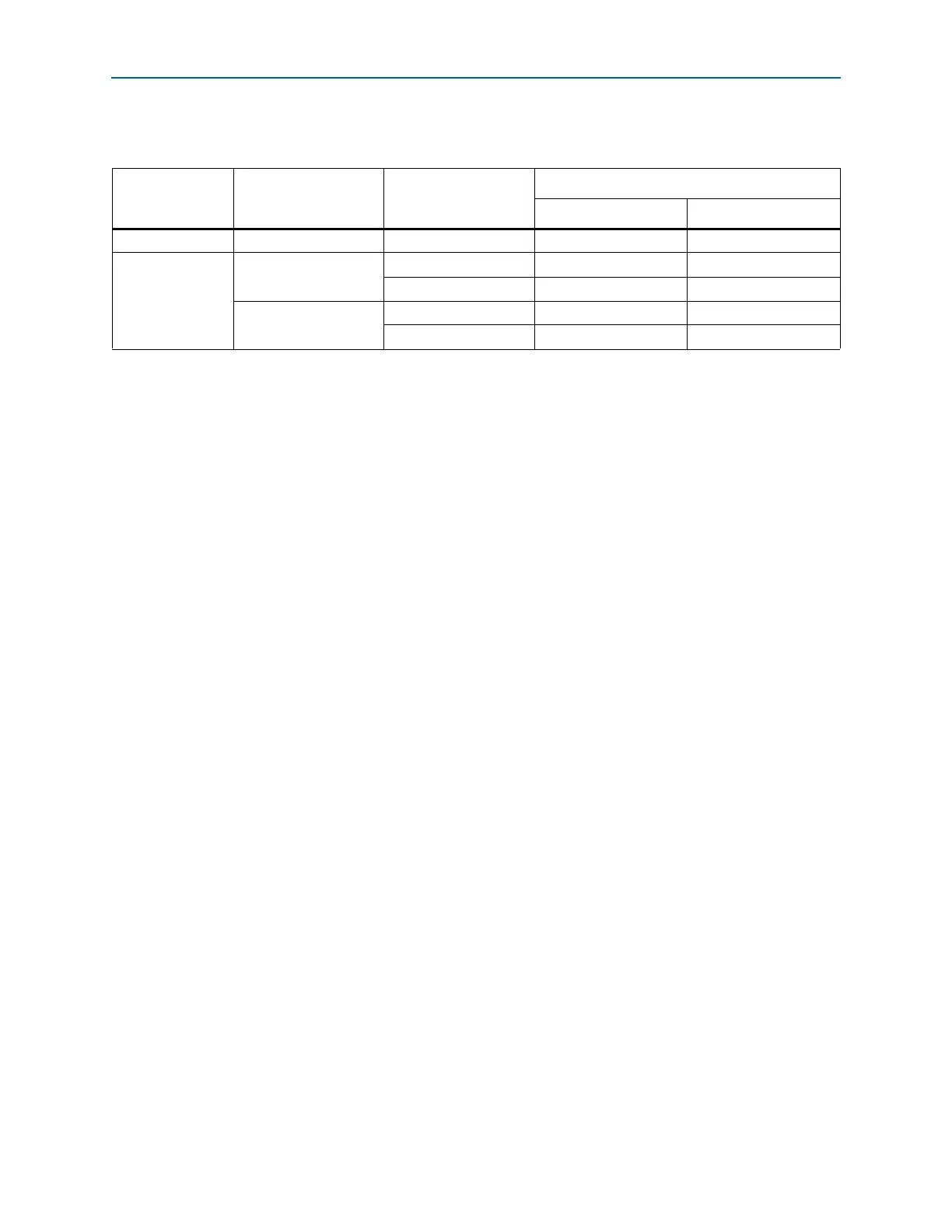

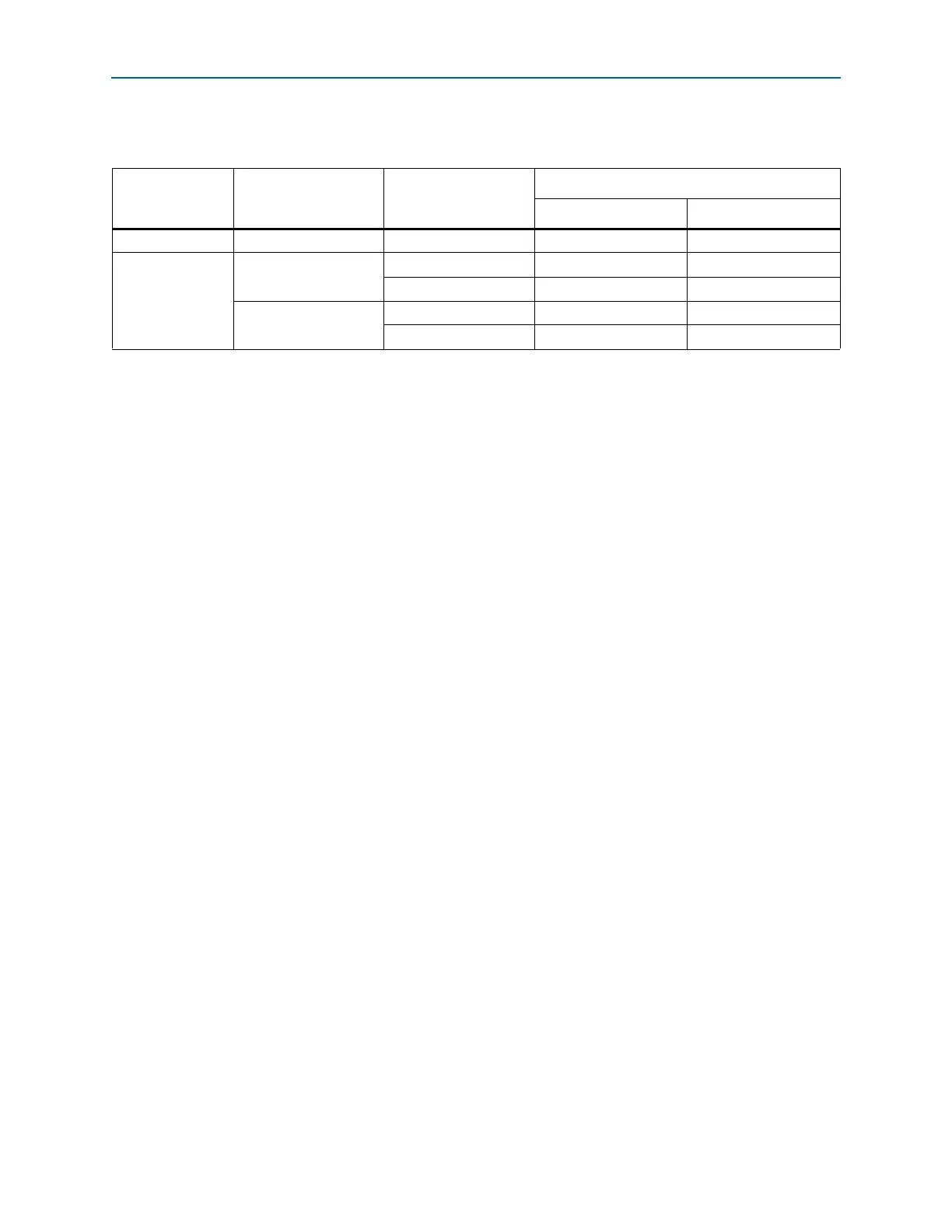

Table 1–9 lists the high- and low-speed clock sources for each channel.

Table 1–9. High- and Low-Speed Clock Sources for Each Channel in Non-Bonded Channel Configuration

Package Transceiver Block Transceiver Channel

High- and Low-Speed Clocks Sources

Option 1 Option 2

F324 and smaller

GXBL0

All channels

MPLL_1 MPLL_2

F484 and larger

GXBL0

Channels 0, 1

MPLL_5/GPLL_1 MPLL_6

Channels 2, 3

MPLL_5 MPLL_6/MPLL_7

(1)

GXBL1

(1)

Channels 0, 1

MPLL_7/MPLL_6 MPLL_8

Channels 2, 3

MPLL_7 MPLL_8/GPLL_2

Note to Table 1–9:

(1)

MPLL_7

and

GXBL1

are not applicable for transceivers in F484 package

Loading...

Loading...