Chapter 3: Cyclone IV Dynamic Reconfiguration 3–23

Dynamic Reconfiguration Modes

November 2011 Altera Corporation Cyclone IV Device Handbook,

Volume 2

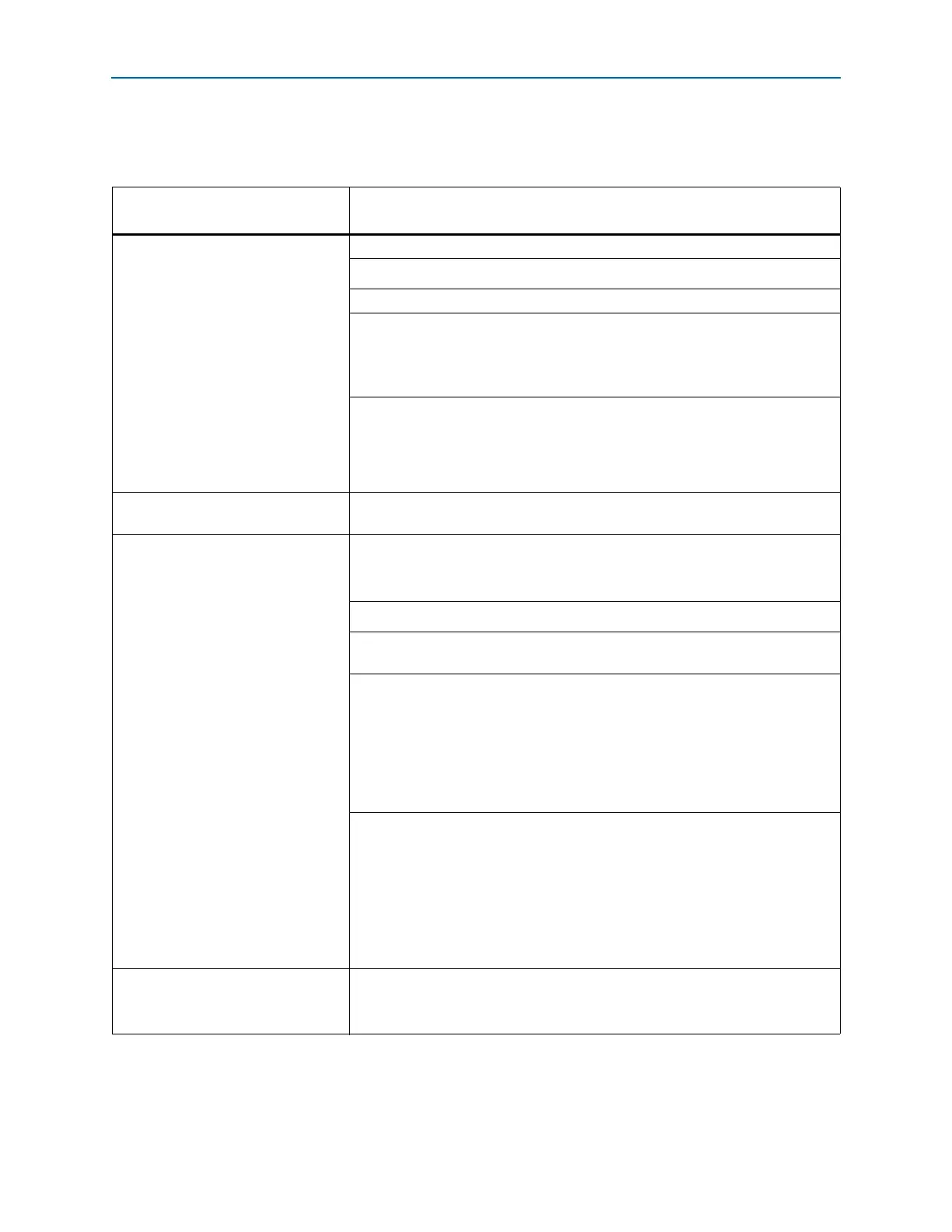

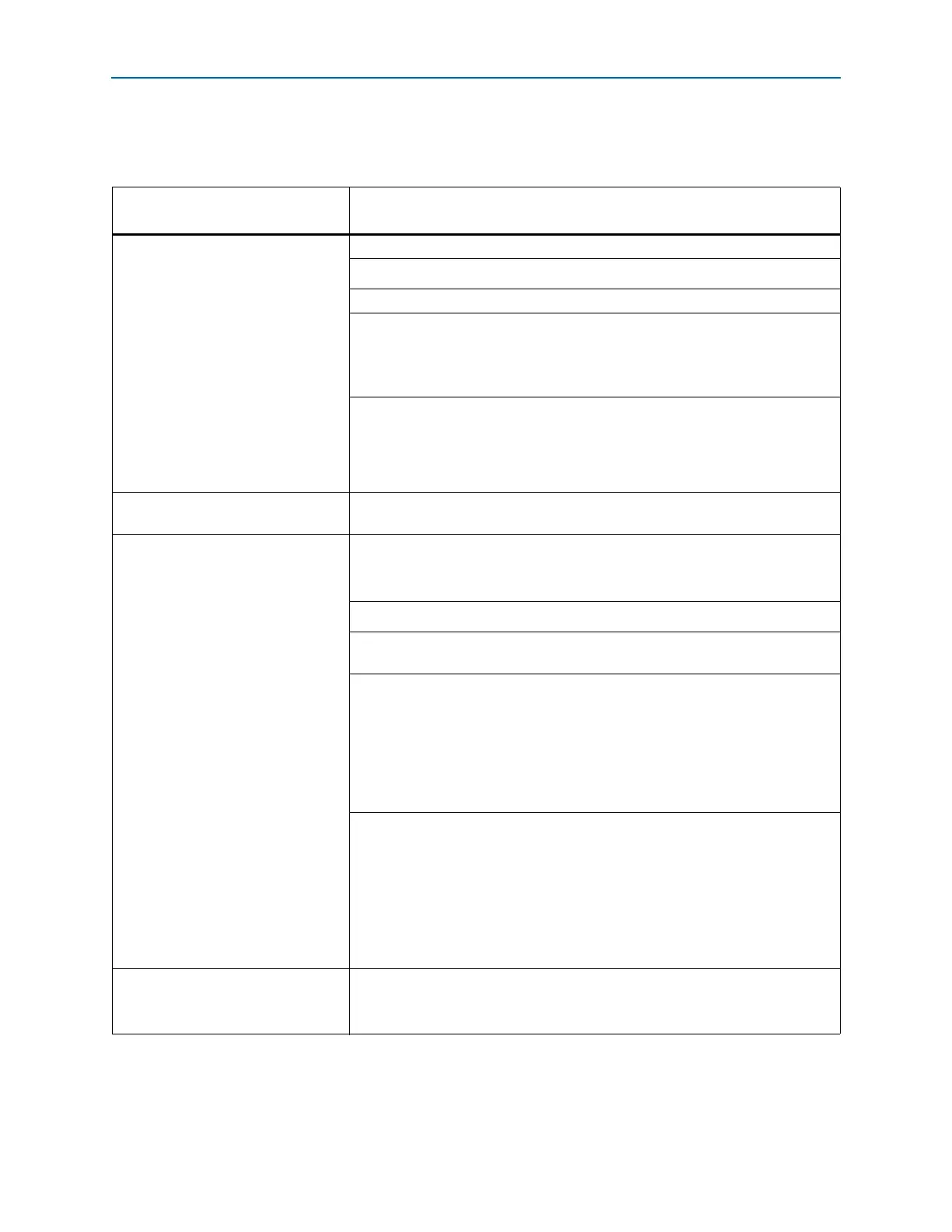

Table 3–4 describes the

tx_datainfull[21..0]

FPGA fabric-transceiver channel

interface signals.

Table 3–4. tx_datainfull[21..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions

(1)

FPGA Fabric-Transceiver Channel

Interface Description

Transmit Signal Description (Based on Cyclone IV GX Supported FPGA

Fabric-Transceiver Channel Interface Widths)

8-bit FPGA fabric-Transceiver Channel

Interface

tx_datainfull[7:0]

: 8-bit data (

tx_datain

)

The following signals are used only in 8B/10B modes:

tx_datainfull[8]

: Control bit (

tx_ctrlenable

)

tx_datainfull[9]

Transmitter force disparity Compliance (PCI Express [PIPE]) (

tx_forcedisp

) in

all modes except PCI Express (PIPE) functional mode. For PCI Express (PIPE)

functional mode, (

tx_forcedispcompliance

) is used.

■ For non-PIPE:

tx_datainfull[10]

: Forced disparity value (

tx_dispval

)

■ For PCIe:

tx_datainfull[10]

: Forced electrical idle (

tx_forceelecidle

)

10-bit FPGA fabric-Transceiver

Channel Interface

tx_datainfull[9:0]

: 10-bit data (

tx_datain

)

16-bit FPGA fabric-Transceiver

Channel Interface with PCS-PMA set

to 8/10 bits

Two 8-bit Data (

tx_datain

)

tx_datainfull[7:0]

-

tx_datain

(LSByte) and

tx_datainfull[18:11]

-

tx_datain

(MSByte)

The following signals are used only in 8B/10B modes:

tx_datainfull[8]

-

tx_ctrlenable

(LSB) and

tx_datainfull[19]

-

tx_ctrlenable

(MSB)

Force Disparity Enable

■ For non-PIPE:

tx_datainfull[9]

-

tx_forcedisp

(LSB) and

tx_datainfull[20]

-

tx_forcedisp

(MSB)

■ For PCIe:

tx_datainfull[9]

-

tx_forcedispcompliance

and

tx_datainfull[20]

- 0

Force Disparity Value

■ For non-PIPE:

tx_datainfull[10]

-

tx_dispval

(LSB) and

tx_datainfull[21]

-

tx_dispval

(MSB)

■ For PCIe:

tx_datainfull[10]

-

tx_forceelecidle

and

tx_datainfull[21]

-

tx_forceelecidle

20-bit FPGA fabric-Transceiver

Channel Interface with PCS-PMA set

to 10 bits

Two 10-bit Data (

tx_datain

)

tx_datainfull[9:0]

-

tx_datain

(LSByte) and

tx_datainfull[20:11]

-

tx_datain

(MSByte)

Note to Table 3–4:

(1) For all transceiver-related ports, refer to the “Transceiver Port Lists” section in the Cyclone IV GX Transceiver Architecture chapter.

Loading...

Loading...