Timer Module (TIM16B8CV3)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 751

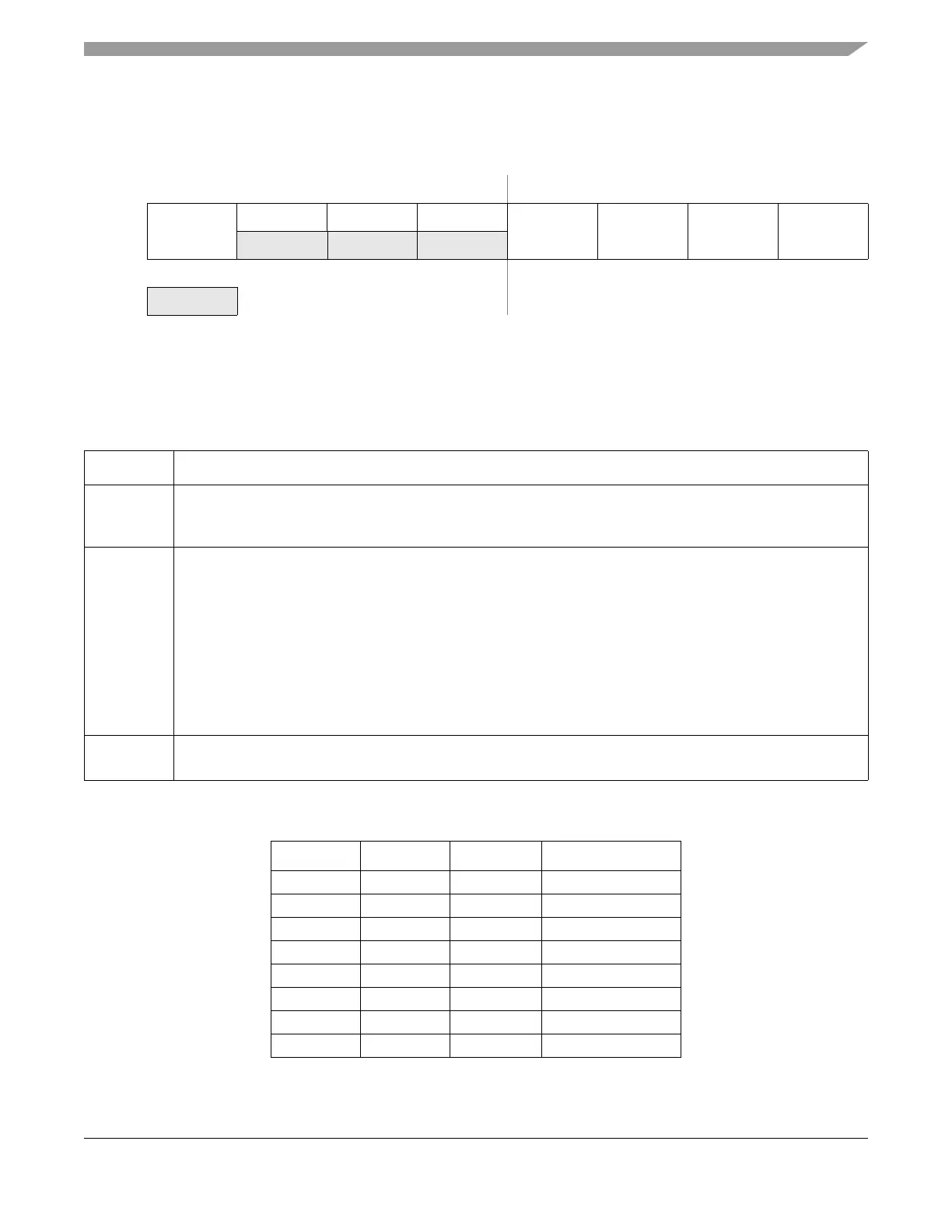

23.3.2.11 Timer System Control Register 2 (TSCR2)

Read: Anytime

Write: Anytime.

Module Base + 0x000D

76543210

R

TOI

000

TCRE PR2 PR1 PR0

W

Reset00000000

= Unimplemented or Reserved

Figure 23-19. Timer System Control Register 2 (TSCR2)

Table 23-14. TSCR2 Field Descriptions

Field Description

7

TOI

Timer Overflow Interrupt Enable

0 Interrupt inhibited.

1 Hardware interrupt requested when TOF flag set.

3

TCRE

Timer Counter Reset Enable — This bit allows the timer counter to be reset by a successful output compare 7

event. This mode of operation is similar to an up-counting modulus counter.

0 Counter reset inhibited and counter free runs.

1 Counter reset by a successful output compare 7.

Note: If TC7 = 0x0000 and TCRE = 1, TCNT will stay at 0x0000 continuously. If TC7 = 0xFFFF and TCRE = 1,

TOF will never be set when TCNT is reset from 0xFFFF to 0x0000.

Note: TCRE=1 and TC7!=0, the TCNT cycle period will be TC7 x "prescaler counter width" + "1 Bus Clock", for

a more detail explanation please refer to Section 23.4.3, “Output Compare

Note: This bit and feature is available only when channel 7 exists. If channel 7 doesn’t exist, this bit is reserved.

Writing to reserved bit has no effect. Read from reserved bit return a zero.

2:0

PR[2:0]

Timer Prescaler Select — These three bits select the frequency of the timer prescaler clock derived from the

Bus Clock as shown in Table 23-15.

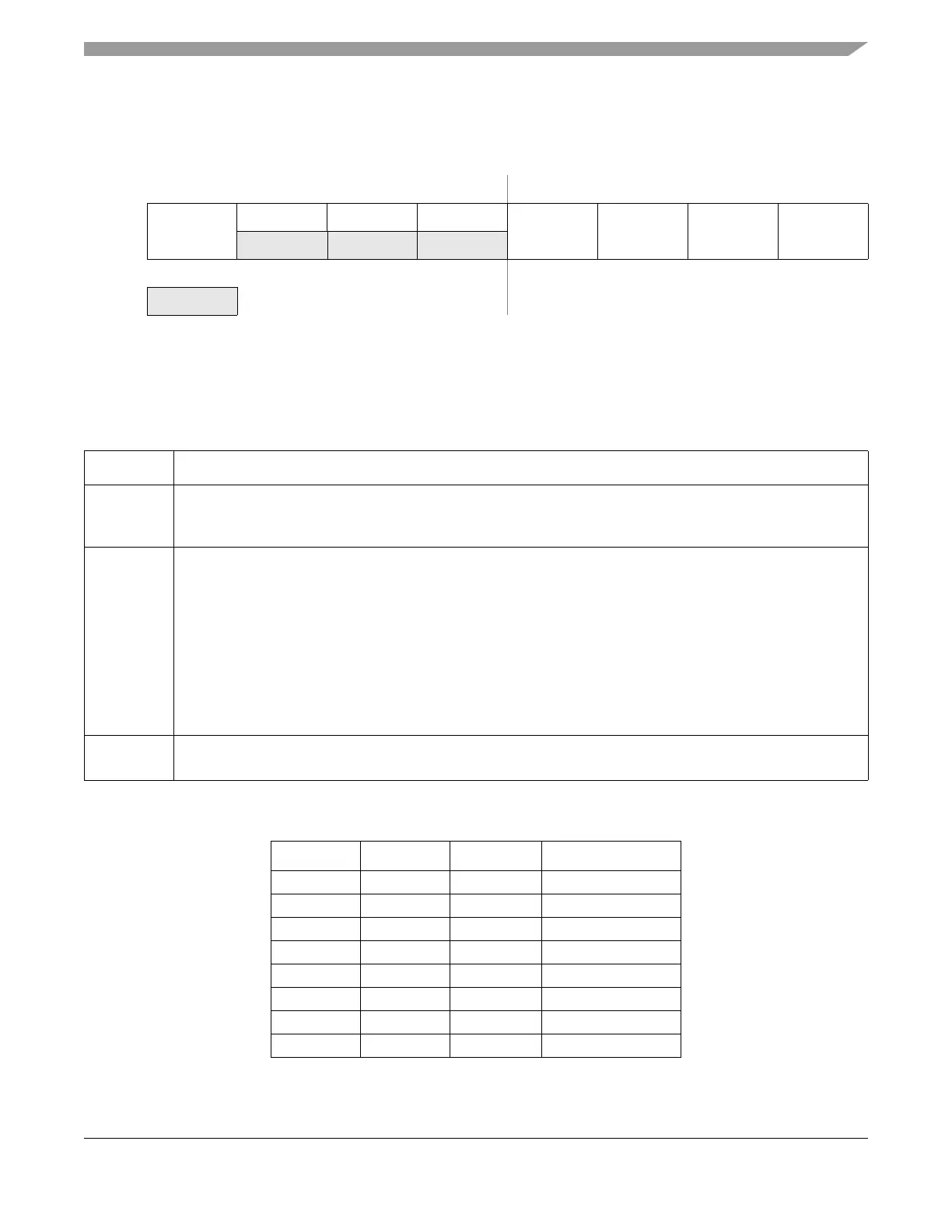

Table 23-15. Timer Clock Selection

PR2 PR1 PR0 Timer Clock

0 0 0 Bus Clock / 1

0 0 1 Bus Clock / 2

0 1 0 Bus Clock / 4

0 1 1 Bus Clock / 8

1 0 0 Bus Clock / 16

1 0 1 Bus Clock / 32

1 1 0 Bus Clock / 64

1 1 1 Bus Clock / 128

Loading...

Loading...