6–26 Chapter 6: I/O Features in Cyclone IV Devices

High-Speed I/O Interface

Cyclone IV Device Handbook, March 2016 Altera Corporation

Volume 1

You can use I/O pins and internal logic to implement a high-speed differential

interface in Cyclone IV devices. Cyclone IV devices do not contain dedicated

serialization or deserialization circuitry. Therefore, shift registers, internal

phase-locked loops (PLLs), and I/O cells are used to perform serial-to-parallel

conversions on incoming data and parallel-to-serial conversion on outgoing data. The

differential interface data serializers and deserializers (SERDES) are automatically

constructed in the core logic elements (LEs) with the Quartus II software ALTLVDS

megafunction.

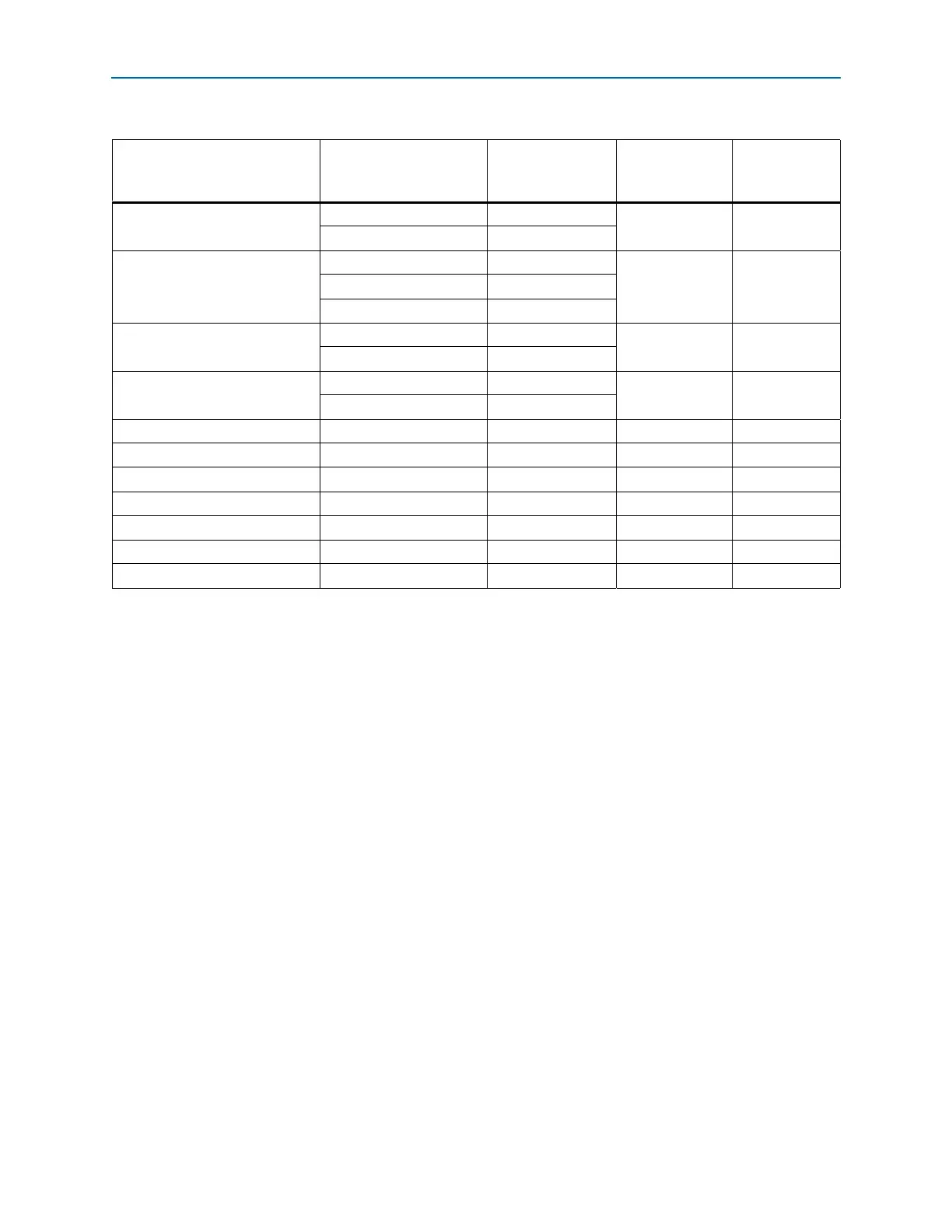

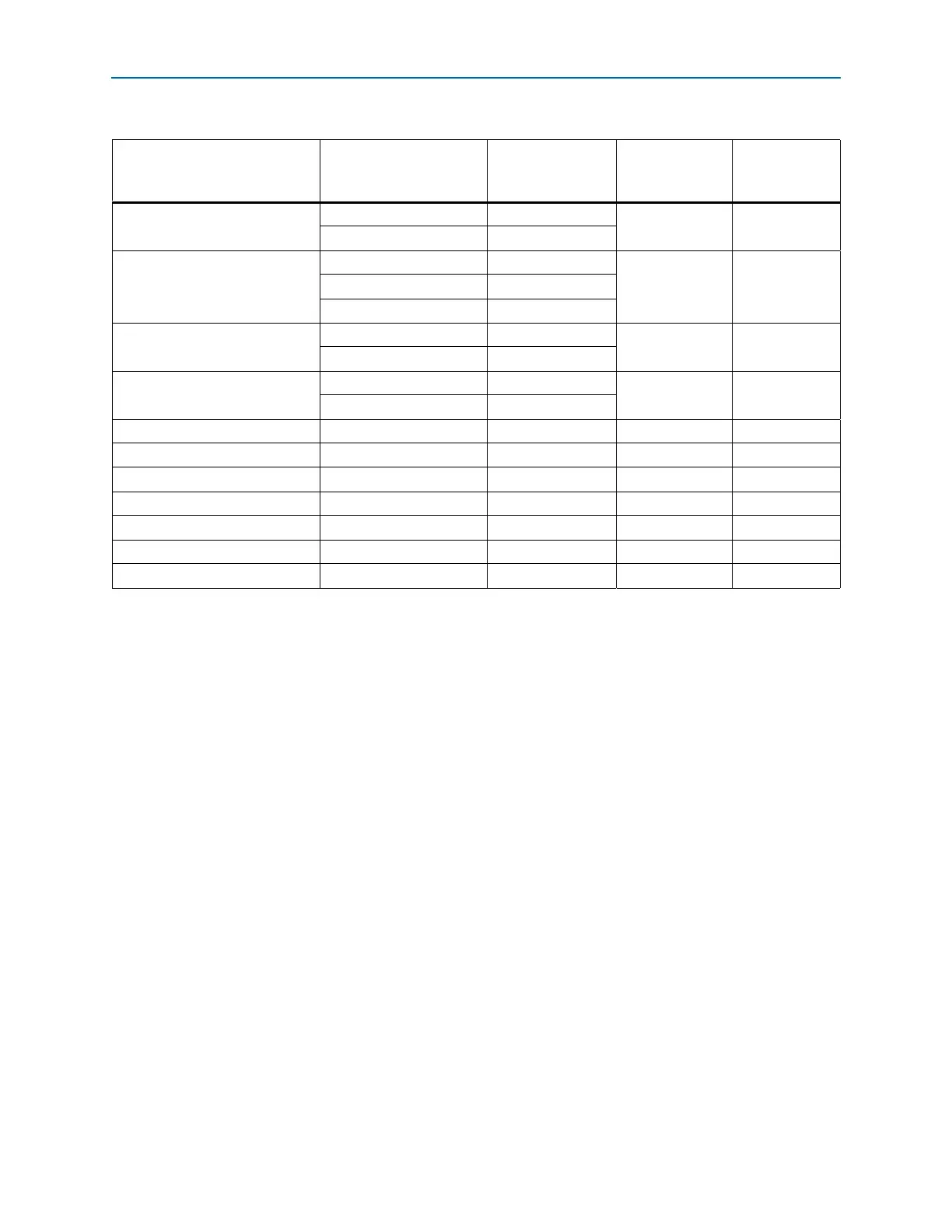

Table 6–7. Differential I/O Standards Supported in Cyclone IV GX I/O Banks

Differential I/O Standards I/O Bank Location

External Resistor

Network at

Transmitter

Transmitter (TX) Receiver (RX)

LVDS

5,6 Not Required

vv

3,4,5,6,7,8 Three Resistors

RSDS

5,6 Not Required

v —3,4,7,8 Three Resistors

3,4,5,6,7,8 Single Resistor

mini-LVDS

5,6 Not Required

v —

3,4,5,6,7,8 Three Resistors

PPDS

5,6 Not Required

v —

3,4,5,6,7,8 Three Resistors

BLVDS

(1)

3,4,5,6,7,8 Single Resistor vv

LVPECL

(2)

3,4,5,6,7,8 — — v

Differential SSTL-2

(3)

3,4,5,6,7,8 — vv

Differential SSTL-18

(3)

3,4,5,6,7,8 — vv

Differential HSTL-18

(3)

3,4,5,6,7,8 — vv

Differential HSTL-15

(3)

3,4,5,6,7,8 — vv

Differential HSTL-12

(3)

4,5,6,7,8 — vv

Notes to Table 6–7:

(1) Transmitter and Receiver f

MAX

depend on system topology and performance requirement.

(2) The LVPECL I/O standard is only supported on dedicated clock input pins.

(3) The differential SSTL-2, SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards are only supported on clock input pins and PLL output clock

pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards.

Loading...

Loading...