8–16 Chapter 8: Configuration and Remote System Upgrades in Cyclone IV Devices

Configuration

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

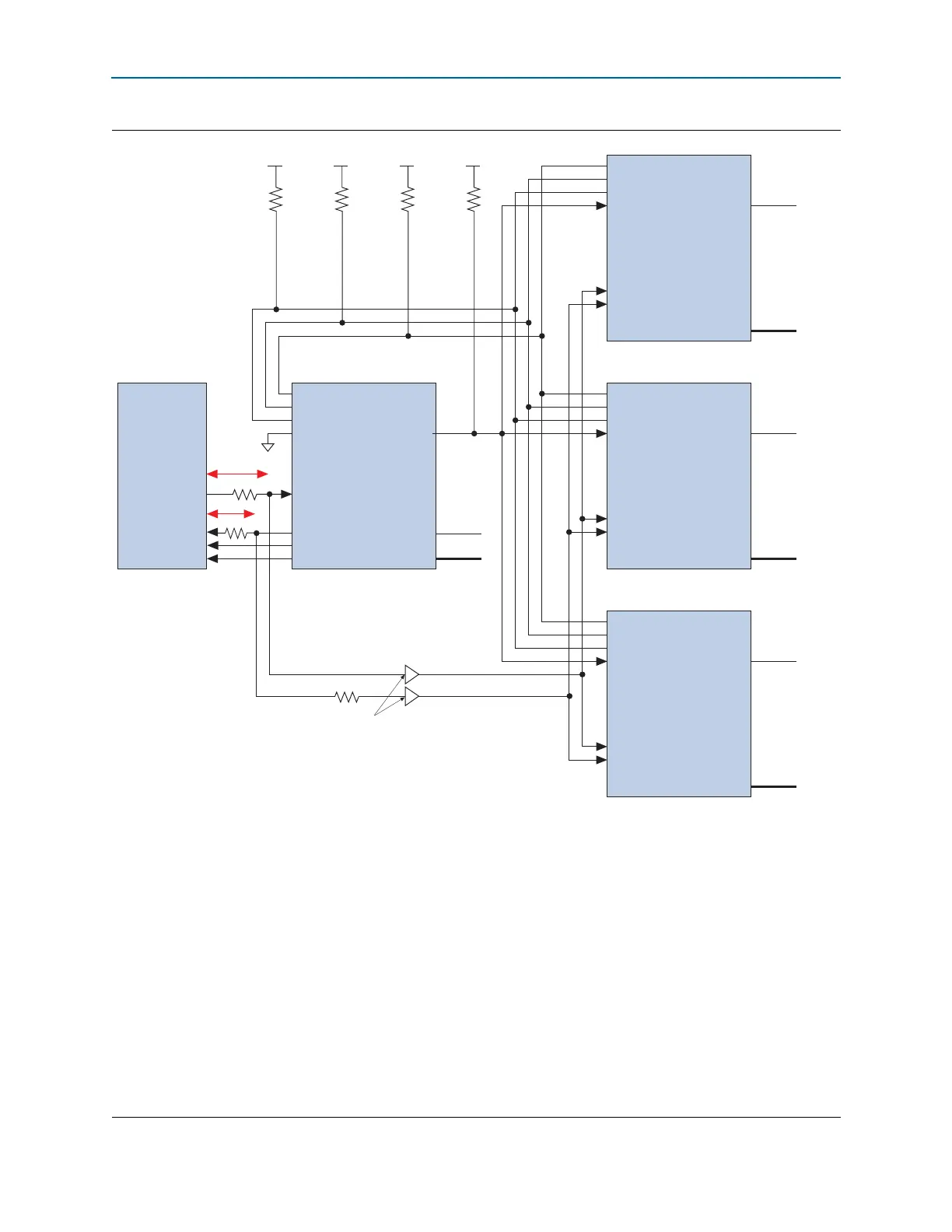

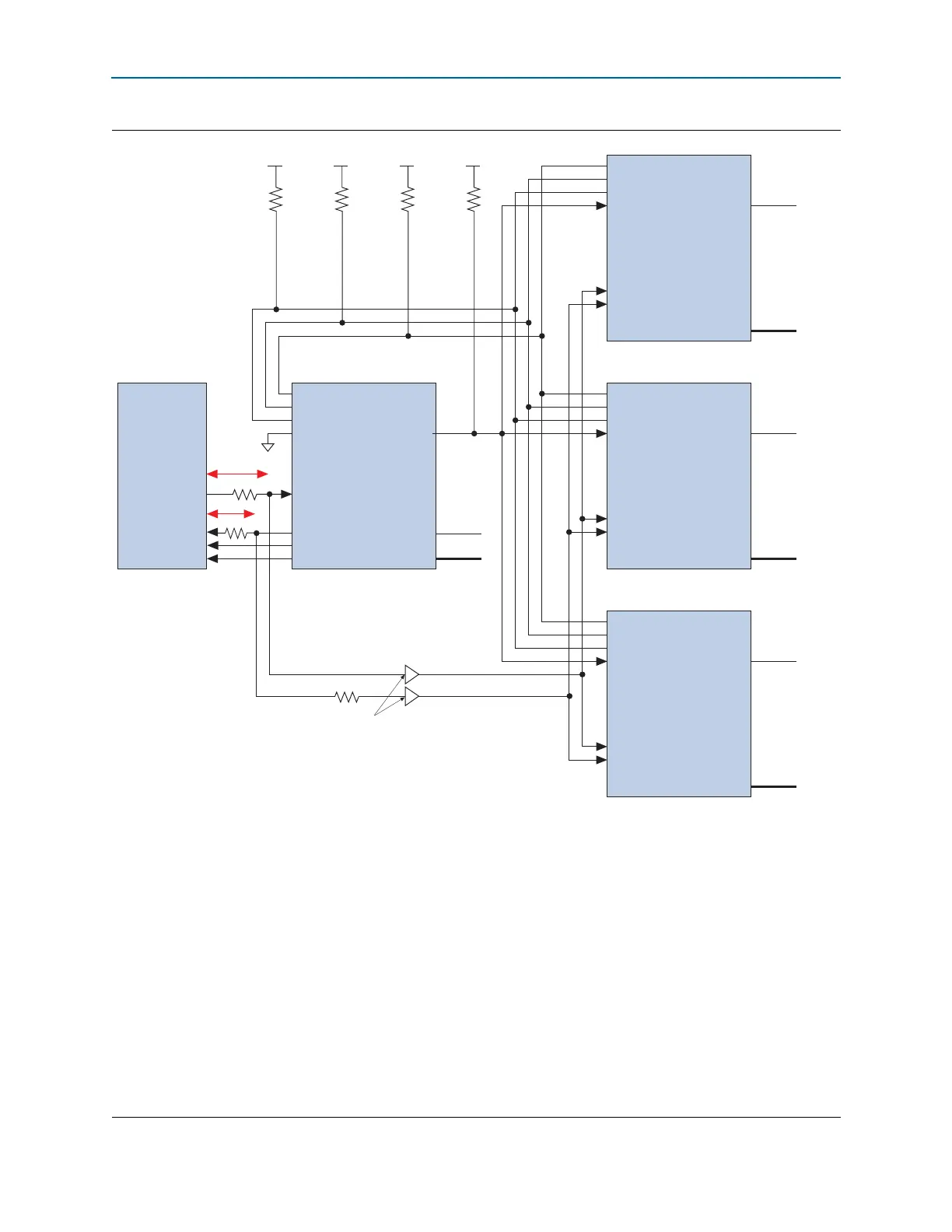

Figure 8–4. Multi-Device AS Configuration in Which Devices Receive the Same Data with Multiple .sof

Notes to Figure 8–4:

(1) Connect the pull-up resistors to the V

CCIO

supply of the bank in which the pin resides.

(2) Connect the pull-up resistor to the V

CCIO

supply voltage of the I/O bank in which the

nCE

pin resides.

(3) The

nCEO

pin is left unconnected or used as a user I/O pin when it does not feed the

nCE

pin of another device.

(4) The

MSEL

pin settings vary for different configuration voltage standards and POR time. You must set the master device in AS mode and the slave

devices in PS mode. To connect the

MSEL

pins for the master device in AS mode and the slave devices in PS mode, refer to Table 8–3 on page 8–8,

Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the

MSEL

pins directly to V

CCA

or GND.

(5) Connect the series resistor at the near end of the serial configuration device.

(6) Connect the repeater buffers between the master and slave devices for

DATA[0]

and

DCLK

. All I/O inputs must maintain a maximum AC voltage

of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in “Configuration and JTAG Pin I/O

Requirements” on page 8–5.

(7) The 50- series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50- series

resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

(8) These pins are dual-purpose I/O pins. The

nCSO

pin functions as

FLASH_nCE

pin in AP mode. The

ASDO

pin functions as

DATA[1]

pin in AP and

FPP modes.

(9) Only Cyclone IV GX devices have an option to select

CLKUSR

(40 MHz maximum) as the external clock source for

DCLK

.

(10) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration

device to the junction-split on both

DCLK

and

Data0

line is 3.5 inches.

nSTATUS

nCONFIG

CONF_DONE

nCE

DATA[0]

DCLK

nCEO

N.C. (3)

(4)

Cyclone IV Slave Device

nSTATUS

nCONFIG

CONF_DONE

nCE

DATA[0]

DCLK

nCEO

N.C. (3)

(4)

V

CCIO

(1)

V

CCIO

(1)

nSTATUS

nCONFIG

CONF_DONE

nCE

DATA[0]

DCLK

nCEO

MSEL[ ]

N.C. (3)

(4)

nSTATUS

nCONFIG

CONF_DONE

nCE

DATA[0]

DCLK

nCSO (8)

ASDO (8)

nCEO

(4) MSEL[ ]MSEL[ ]

MSEL[ ]

DATA

DCLK

nCS

ASDI

Serial Configuration

Device

GND

V

CCIO

(1)

V

CCIO

(2)

10 kΩ

10 kΩ

10 kΩ

10 kΩ

(5)

25

Ω

(5),

50

Ω

(7)

Buffers (6)

(7)

50

Ω

Cyclone IV Slave Device

Cyclone IV Slave Device

Cyclone IV Master Device

CLKUSR

(9)

(10)

(10)

Loading...

Loading...