Chapter 8: Configuration and Remote System Upgrades in Cyclone IV Devices 8–49

Configuration

May 2013 Altera Corporation Cyclone IV Device Handbook,

Volume 1

You can perform JTAG testing on Cyclone IV devices before, during, and after

configuration. Cyclone IV devices support the

BYPASS

,

IDCODE

, and

SAMPLE

instructions during configuration without interrupting configuration. All other JTAG

instructions can only be issued by first interrupting configuration and

reprogramming I/O pins with the

ACTIVE_DISENGAGE

and

CONFIG_IO

instructions.

The

CONFIG_IO

instruction allows you to configure the I/O buffers through the JTAG

port and interrupts configuration when issued after the

ACTIVE_DISENGAGE

instruction. This instruction allows you to perform board-level testing prior to

configuring the Cyclone IV device or waiting for a configuration device to complete

configuration. Prior to issuing the

CONFIG_IO

instruction, you must issue the

ACTIVE_DISENGAGE

instruction. This is because in Cyclone IV devices, the

CONFIG_IO

instruction does not hold

nSTATUS

low until reconfiguration, so you must disengage

the active configuration mode controller when active configuration is interrupted.

The

ACTIVE_DISENGAGE

instruction places the active configuration mode controllers in

an idle state prior to JTAG programming. Additionally, the

ACTIVE_ENGAGE

instruction

allows you to re-engage a disengaged active configuration mode controller.

1 You must follow a specific flow when executing the

ACTIVE_DISENGAGE

,

CONFIG_IO

,

and

ACTIVE_ENGAGE

JTAG instructions in Cyclone IV devices.

The chip-wide reset (

DEV_CLRn

) and chip-wide output enable (

DEV_OE

) pins in

Cyclone IV devices do not affect JTAG boundary-scan or programming operations.

Toggling these pins do not affect JTAG operations (other than the usual

boundary-scan operation).

When designing a board for JTAG configuration of Cyclone IV devices, consider the

dedicated configuration pins. Table 8–15 describes how you must connect these pins

during JTAG configuration.

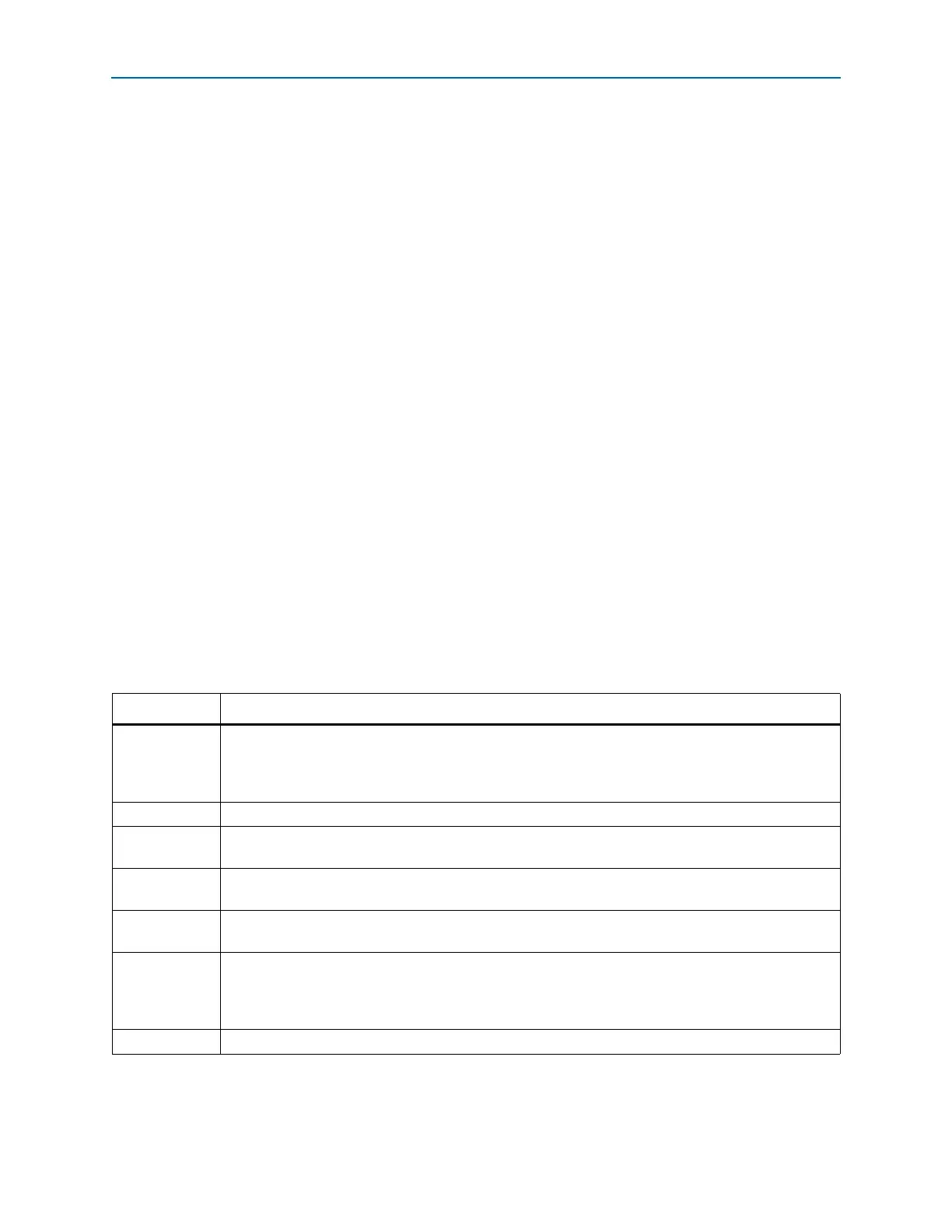

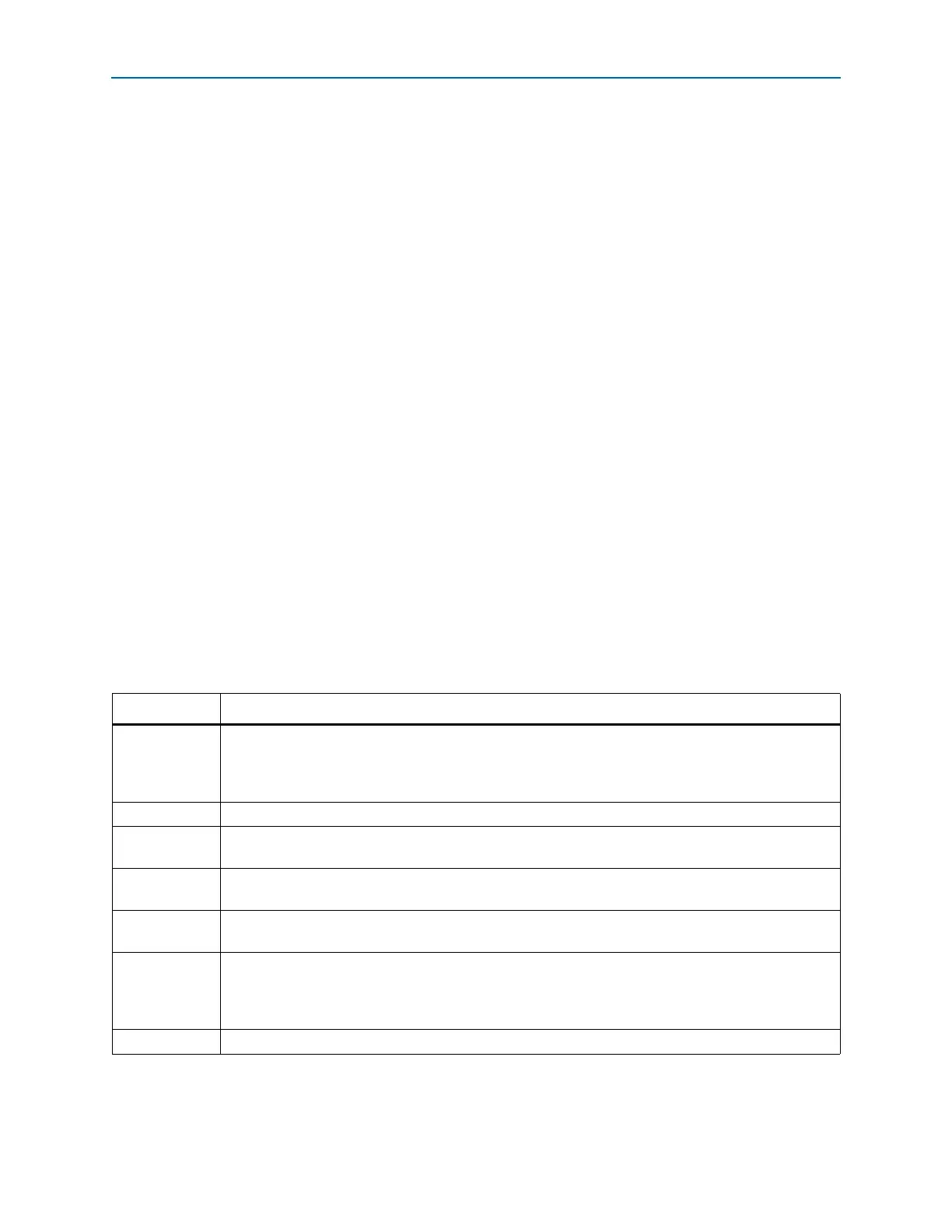

Table 8–15. Dedicated Configuration Pin Connections During JTAG Configuration

Signal Description

nCE

On all Cyclone IV devices in the chain,

nCE

must be driven low by connecting it to GND, pulling it low

through a resistor, or driving it by some control circuitry. For devices that are also in multi-device AS, AP,

PS, or FPP configuration chains, you must connect the

nCE

pins to GND during JTAG configuration or

JTAG configured in the same order as the configuration chain.

nCEO

On all Cyclone IV devices in the chain,

nCEO

is left floating or connected to the

nCE

of the next device.

MSEL

These pins must not be left floating. These pins support whichever non-JTAG configuration that you used

in production. If you only use JTAG configuration, tie these pins to GND.

nCONFIG

Driven high by connecting to the V

CCIO

supply of the bank in which the pin resides and pulling up through

a resistor or driven high by some control circuitry.

nSTATUS

Pull to the V

CCIO

supply of the bank in which the pin resides through a 10-k resistor. When configuring

multiple devices in the same JTAG chain, each

nSTATUS

pin must be pulled up to the V

CCIO

individually.

CONF_DONE

Pull to the V

CCIO

supply of the bank in which the pin resides through a 10-k resistor. When configuring

multiple devices in the same JTAG chain, each

CONF_DONE

pin must be pulled up to V

CCIO

supply of the

bank in which the pin resides individually.

CONF_DONE

going high at the end of JTAG configuration

indicates successful configuration.

DCLK

Must not be left floating. Drive low or high, whichever is more convenient on your board.

Loading...

Loading...