Altera Corporation 4–1

June 2006

4. Selectable I/O Standards

in Stratix &

Stratix GX Devices

Introduction

The proliferation of I/O standards and the need for higher I/O

performance have made it critical that devices have flexible I/O

capabilities. Stratix

®

and Stratix GX programmable logic devices (PLDs)

feature programmable I/O pins that support a wide range of industry

I/O standards, permitting increased design flexibility. These I/O

capabilities enable fast time-to-market and high-performance solutions to

meet the demands of complex system designs. Additionally, Stratix and

Stratix GX devices simplify system board design and make it easy to

connect to microprocessors, peripherals, memories, gate arrays,

programmable logic circuits, and standard logic functions.

This chapter provides guidelines for using one or more industry I/O

standards in Stratix and Stratix GX devices, including:

■ Stratix and Stratix GX I/O standards

■ High-speed interfaces

■ Stratix and Stratix GX I/O banks

■ Programmable current drive strength

■ Hot socketing

■ Differential on-chip termination

■ I/O pad placement guidelines

■ Quartus

®

II software support

Stratix & Stratix

GX I/O

Standards

Stratix and Stratix GX devices support a wide range of industry I/O

standards as shown in the Stratix Device Family Data Sheet section in the

Stratix Device Handbook, Volume 1 and the Stratix GX Device Family Data

Sheet section of the Stratix GX Device Handbook, Volume 1. Several

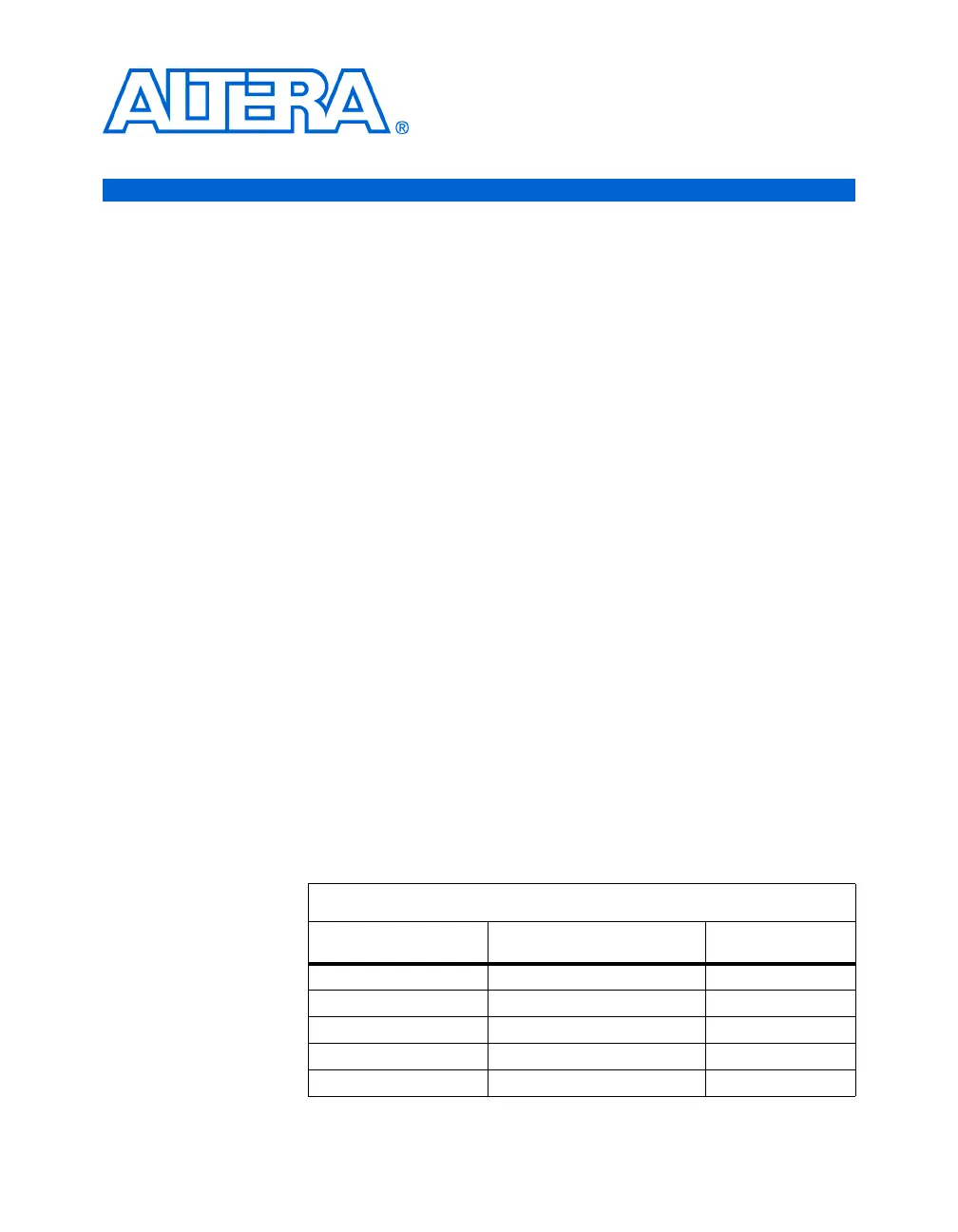

applications that use these I/O standards are listed in Table 4–1.

Table 4–1. I/O Standard Applications & Performance (Part 1 of 2) Note (1)

I/O Standard Application Performance

3.3-V LVTTL/LVCMOS General purpose 350 MHz

2.5-V LVTTL/LVCMOS General purpose 350 MHz

1.8-V LVTTL/LVCMOS General purpose 250 MHz

1.5-V LVCMOS General purpose 225 MHz

PCI/CompactPCI PC/embedded systems 66 MHz

S52004-3.4

Loading...

Loading...