Altera Corporation 8–5

July 2005 Stratix Device Handbook, Volume 2

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

Interfaces

The following sections discuss XSBI, PCS, XGMII, and XAUI.

XSBI

One of the blocks of 10-Gigabit Ethernet is the XSBI interface. XSBI is the

interface between the PCS and the PMA sublayers of the PHY layer of the

OSI model. XSBI supports two types of PHY layers, LAN PHY and WAN

PHY. The LAN PHY is part of 10GBASE-R, and supports existing

Gigabit Ethernet applications at ten times the bandwidth. The WAN PHY

is part of 10GBASE-W, and supports connections to existing and future

installations of SONET/SDH circuit-switched access equipment.

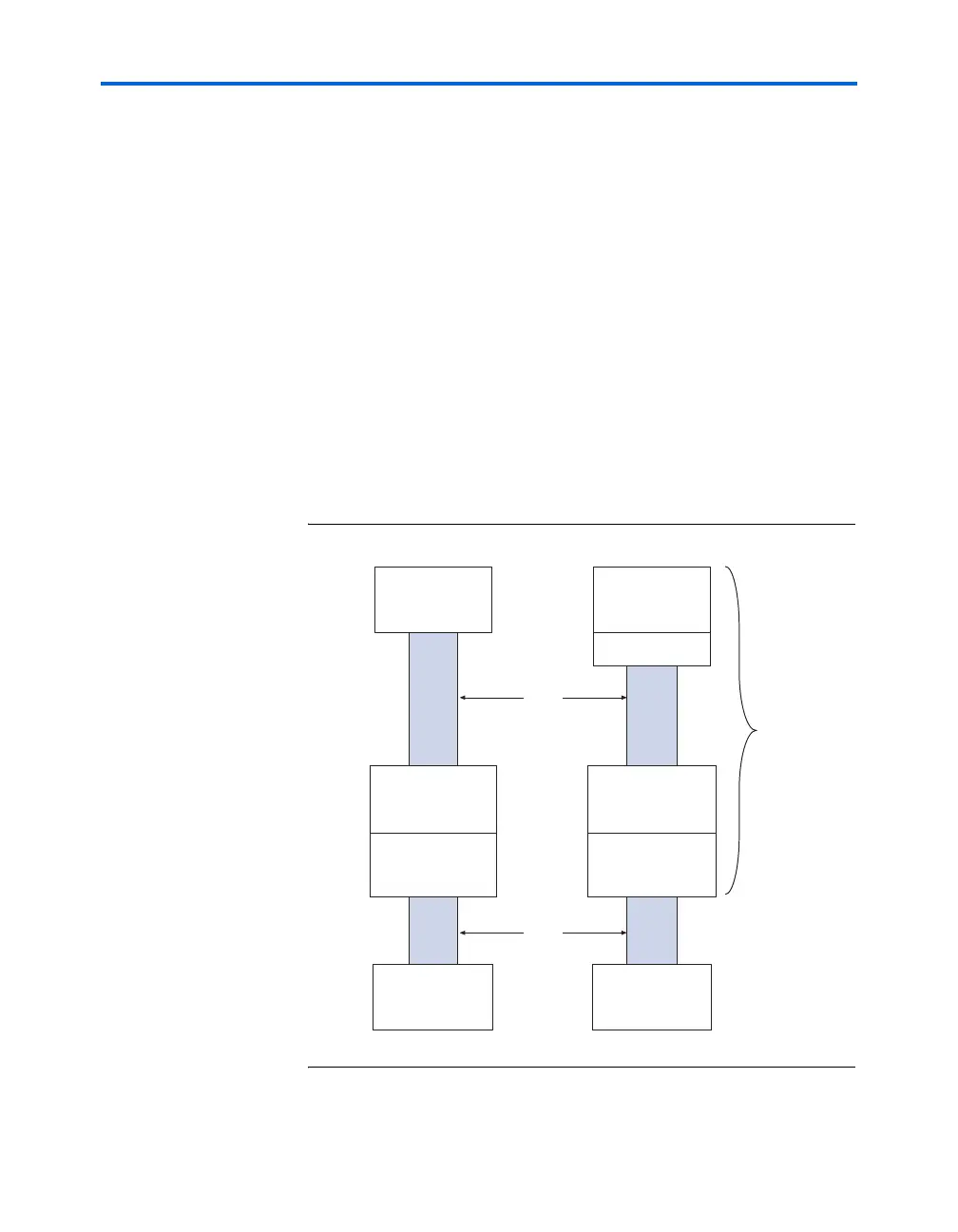

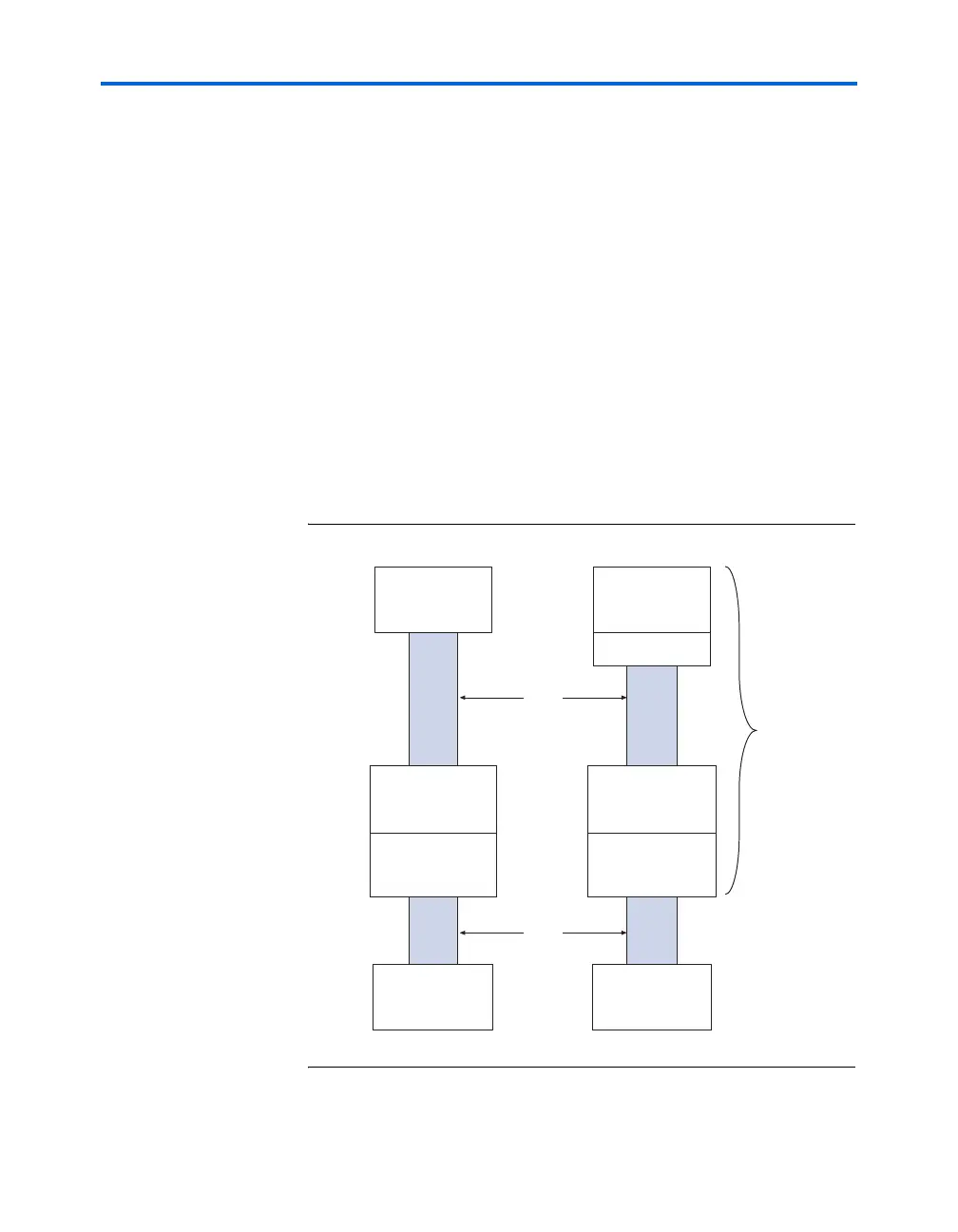

10GBASE-R is a physical layer implementation that is comprised of the

PCS sublayer, the PMA, and the PMD. 10GBASE-R is based upon

64b/66b data coding. 10GBASE-W is a PHY layer implementation that is

comprised of the PCS sublayer, the WAN interface sublayer (WIS), the

PMA, and the PMD. 10GBASE-W is based on STS-192c/SDH VC-4-64c

encapsulation of 64b/66b encoded data. Figure 8–3 shows the

construction of these two PHY layers.

Figure 8–3. XSBI Interface for the Two PHY Layers

PCS

PMA

PMD

Medium

PCS

PMA

PMD

Medium

WIS

XSBI

MDI

10GBASE-R 10GBASE-W

PHY

Loading...

Loading...