Altera Corporation 1–41

July 2005 Stratix Device Handbook, Volume 2

General-Purpose PLLs in Stratix & Stratix GX Devices

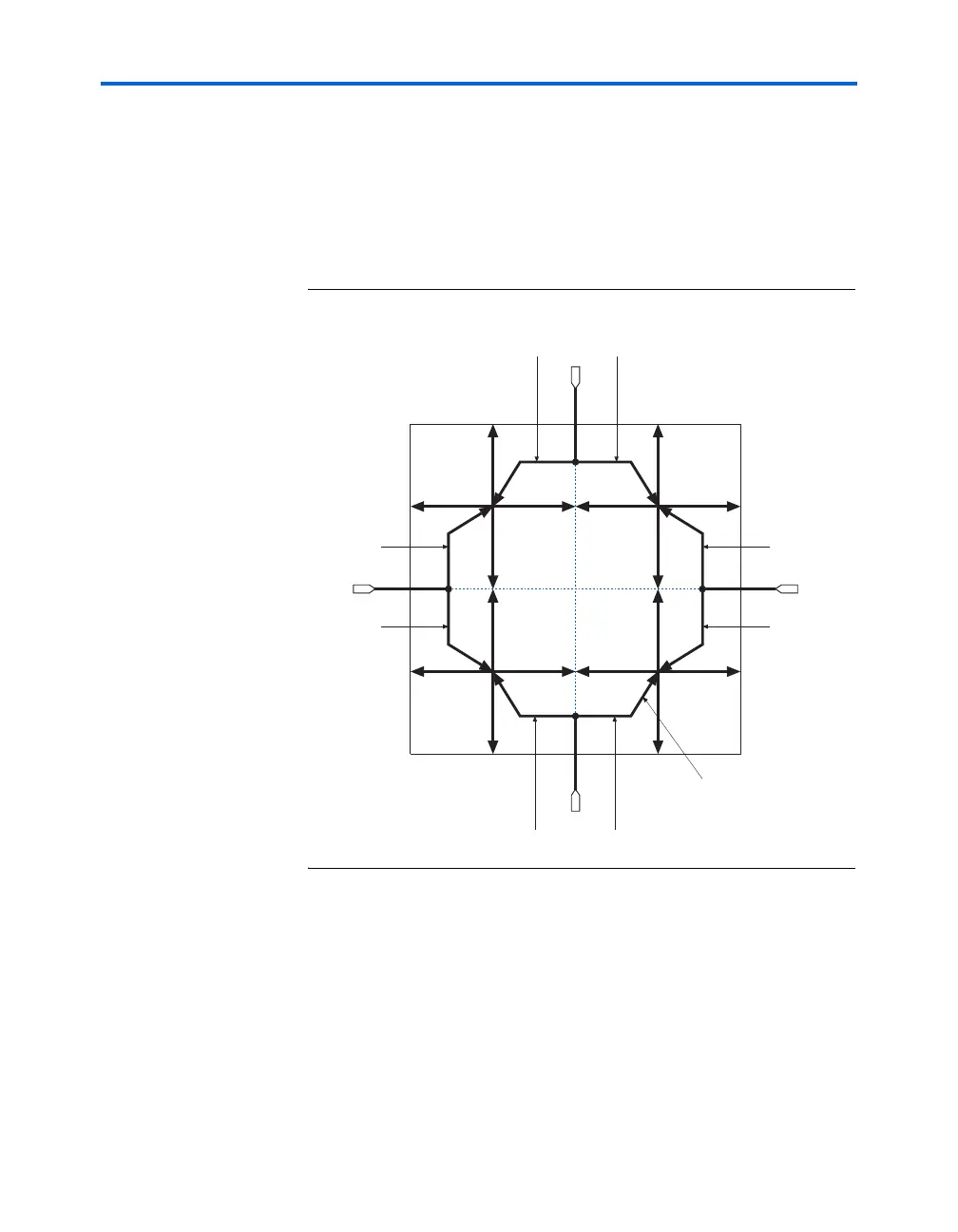

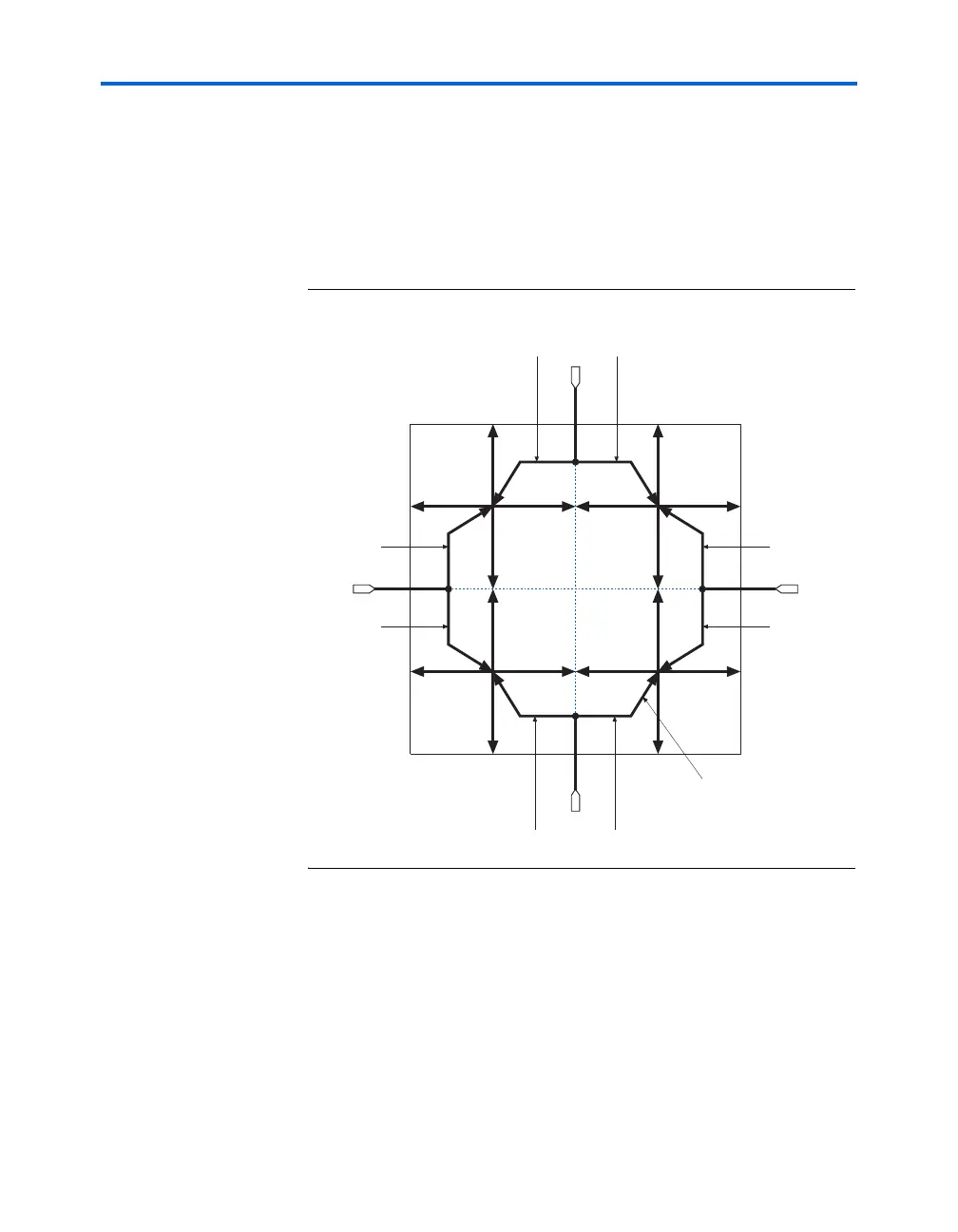

RCLK[12..15] are in the bottom-right quadrant. The regional clock

networks only pertain to the quadrant they drive into. The regional clock

networks provide the lowest clock delay and skew for logic contained

within a single quadrant. RCLK clock networks cannot be driven by

internal logic. The CLK clock pins symmetrically drive the RCLK networks

within a particular quadrant, as shown in Figure 1–20. See Figures 1–21

and 1–22 for RCLK connections from PLLs and CLK pins.

Figure 1–20. Regional Clocks

Clock Input Connections

Two CLK pins drive each enhanced PLL. You can use either one or both

pins for clock switchover inputs into the PLL. Either pin can be the

primary clock source for clock switchover, which is controlled in the

Quartus II software. Enhanced PLLs 5 and 6 also have feedback input

pins as shown in Table 1–14.

RCLK[1..0]

RCLK[4..5]

RCLK[6..7] RCLK[12..13]

RCLK[2..3] RCLK[11..10]

RCLK[14..15]

RCLK[9..8]

CLK[15..12]

CLK[3..0]

CLK[7..4]

CLK[11..8]

Regional Clocks Only Drive a Device

Quadrant from Specified CLK Pins or

PLLs within that Quadrant

Loading...

Loading...