Altera Corporation 5–47

July 2005 Stratix Device Handbook, Volume 2

High-Speed Differential I/O Interfaces in Stratix Devices

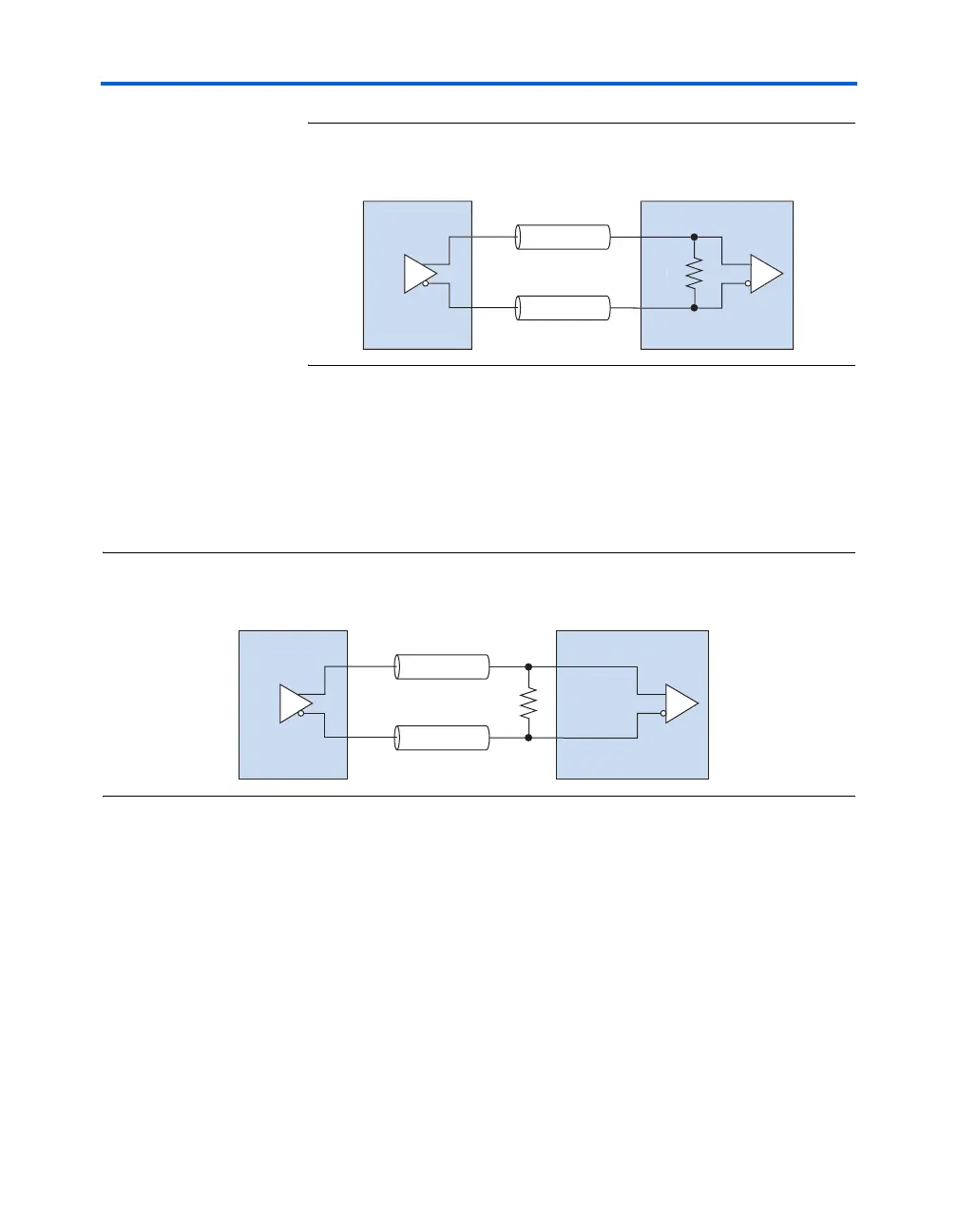

Figure 5–33. LVDS Differential On-Chip Termination

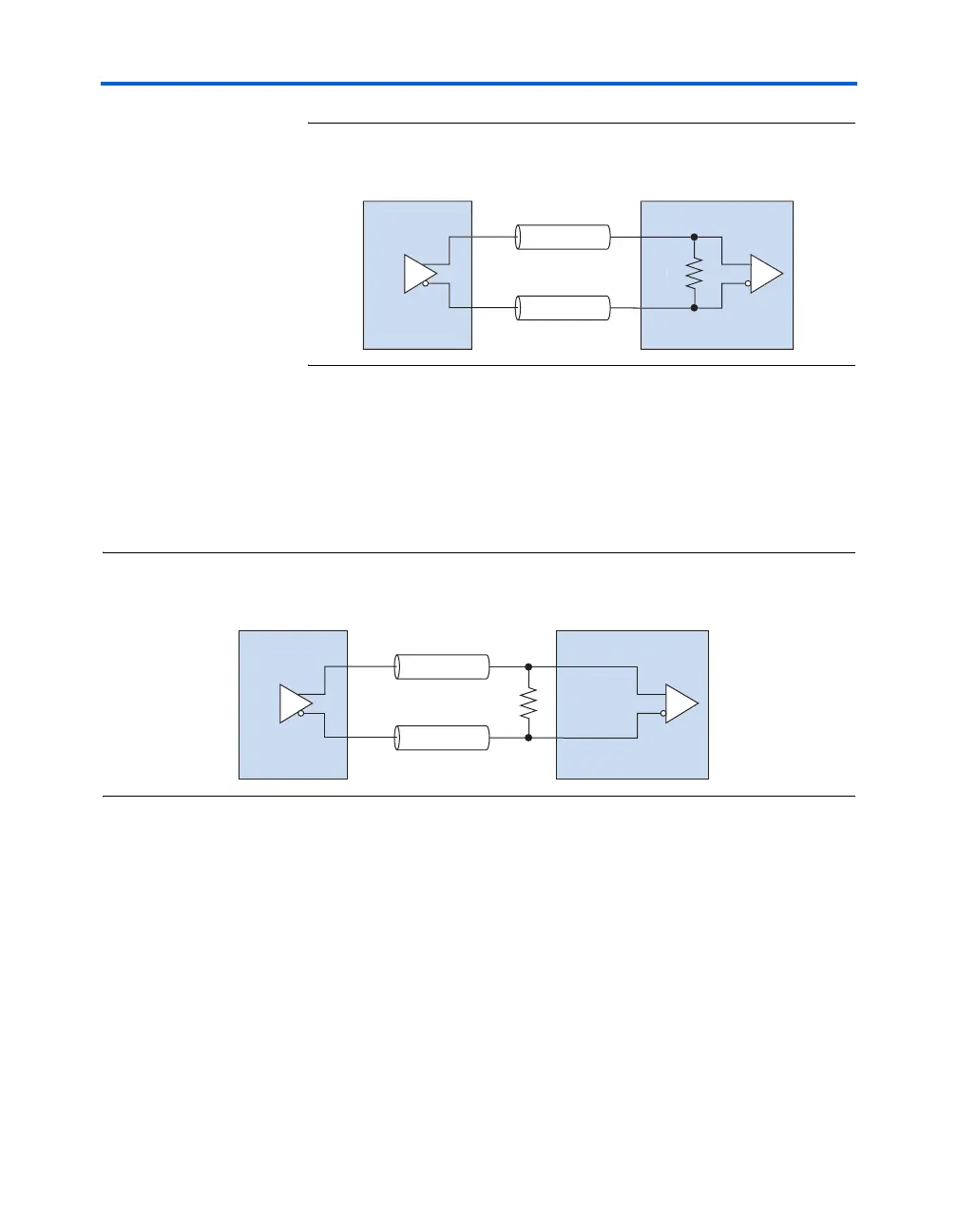

HyperTransport & LVPECL Differential Termination

HyperTransport and LVPECL I/O standards are terminated by an

external 100-Ω resistor on the input pin. Figure 5–34 shows the device

with differential termination for the HyperTransport or LVPECL I/O

standard.

Figure 5–34. HyperTransport & LVPECL Differential Termination

PCML Differential Termination

The PCML I/O technology is an alternative to the LVDS I/O technology,

and use an external voltage source (V

TT

), a pair of 100-Ω resistors on the

input side and a pair of 50-Ω resistors on the output side. Figure 5–35

shows the device with differential termination for PCML I/O standard.

LVDS Transmitter

LVDS Receiver with

On-Chi

100

Ω Termination

Z

0

=

Z

0

=

R

D

Differential

Transmitter

Differential Receiver

Z

0

= 50 Ω

Z

0

= 50 Ω

Loading...

Loading...