7–62 Altera Corporation

Stratix Device Handbook, Volume 2 September 2004

Conclusion

Arithmetic Function Implementation Results

Table 7–19 shows the results of the implementation shown in Figure 7–38

with the PIPELINE parameter set to YES. Table 7–20 shows the results of

the implementation shown in Figure 7–38 with the PIPELINE parameter

set to NO.

Arithmetic Function Design Example

Download the Vector Magnitude Function (magnitude.zip) design

example from the Design Examples section of the Altera web site at

www.altera.com.

Conclusion

The DSP blocks in Stratix and Stratix GX devices are optimized to support

DSP functions requiring high data throughput, such as FIR filters, IIR

filters and the DCT. The DSP blocks are flexible and configurable in

different operation modes based on the application’s needs. The

TriMatrix memory provides the data storage capability often needed in

DSP applications.

The DSP blocks and TriMatrix memory in Stratix and Stratix GX devices

offer performance and flexibility that translates to higher performance

DSP functions.

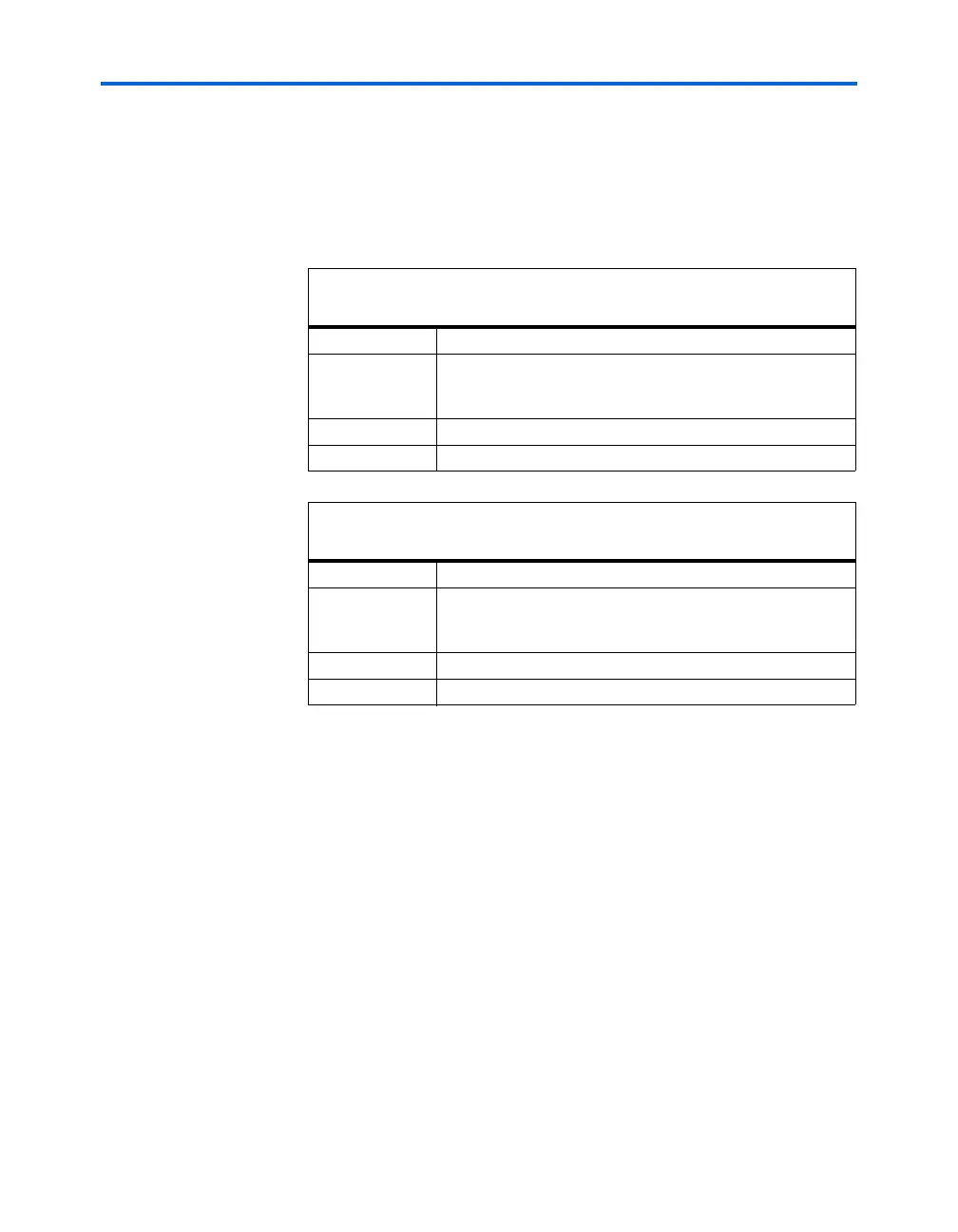

Table 7–19. Vector Magnitude Function Implementation Results

(PIPELINE=YES)

Part EP1S10F780

Utilization Lcell: 497/10570 (4%)

DSP block 9-bit elements: 2/48 (4%)

Memory bits: 0/920448 (0%)

Performance 194 MHz

Latency 15 clock cycles

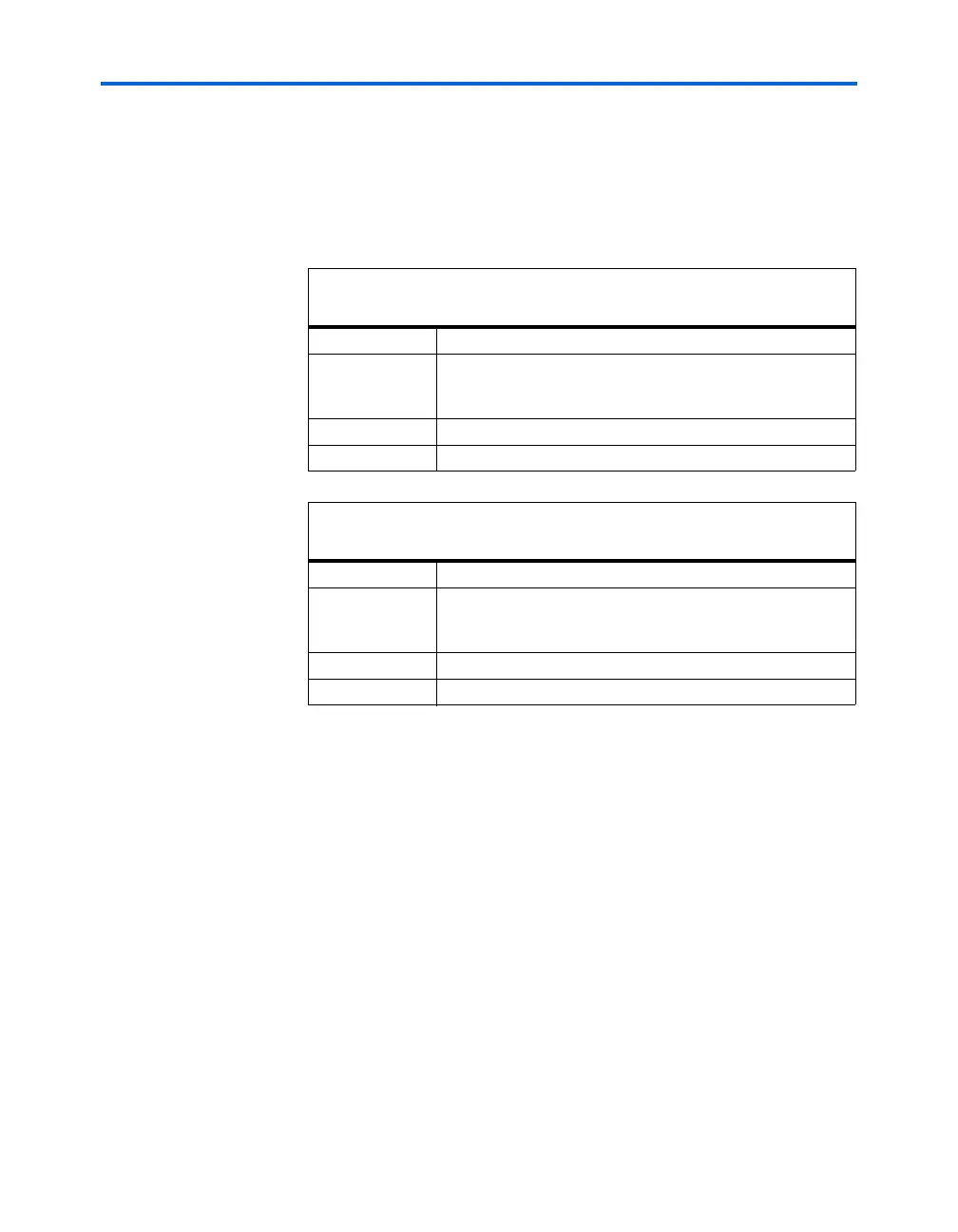

Table 7–20. Vector Magnitude Function Implementation Results

(PIPELINE=NO)

Part EP1S10F780

Utilization Lcell: 244/10570 (2%)

DSP block 9-bit elements: 2/48 (4%)

Memory bits: 0/920448 (0%)

Performance 30 MHz

Latency 3 clock cycles

Loading...

Loading...