Altera Corporation 1–1

July 2005

1. General-Purpose PLLs in

Stratix & Stratix GX Devices

Introduction

Stratix

®

and Stratix GX devices have highly versatile phase-locked loops

(PLLs) that provide robust clock management and synthesis for on-chip

clock management, external system clock management, and high-speed

I/O interfaces. There are two types of PLLs in each Stratix and Stratix GX

device: enhanced PLLs and fast PLLs. Each device has up to four

enhanced PLLs, which are feature-rich, general-purpose PLLs supporting

advanced capabilities such as external feedback, clock switchover, phase

and delay control, PLL reconfiguration, spread spectrum clocking, and

programmable bandwidth. There are also up to eight fast PLLs per

device, which offer general-purpose clock management with

multiplication and phase shifting as well as high-speed outputs to

manage the high-speed differential I/O interfaces.

The Altera

®

Quartus

®

II software enables the PLLs and their features

without requiring any external devices.

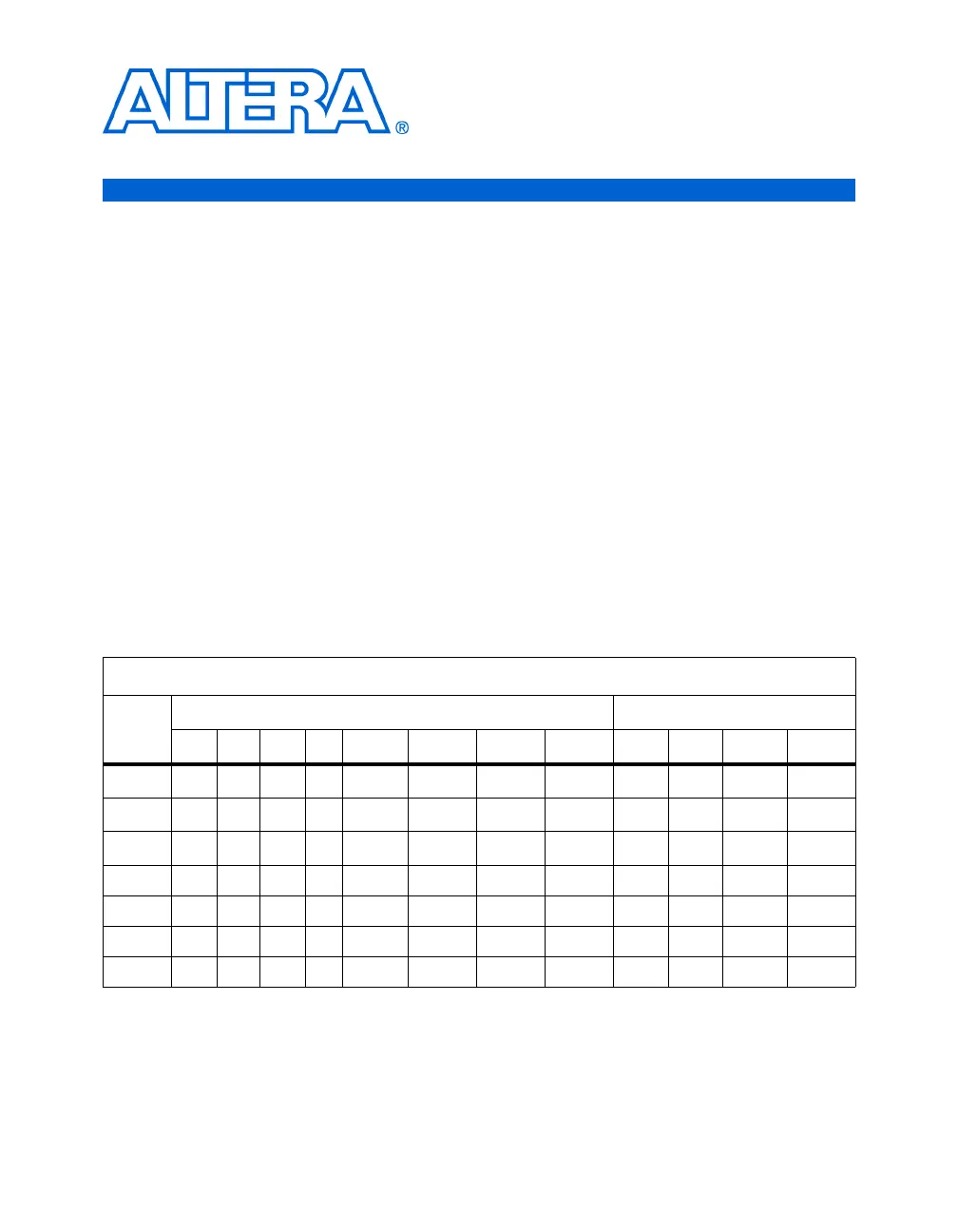

Tables 1–1 and 1–2 show PLL availability for Stratix and Stratix GX

devices, respectively.

Table 1–1. Stratix Device PLL Availability

Device

Fast PLLs Enhanced PLLs

1234 7 8 9 10 5(1) 6(1) 11(2) 12(2)

EP1S10

vvvv v v

EP1S20

vvvv v v

EP1S25

vvvv v v

EP1S30

vvvvv (3) v (3) v (3) v (3) vv

EP1S40

vvvvv (3) v (3) v (3) v (3) vvv (3) v (3)

EP1S60

vvvv v v v v v v v v

EP1S80

vvvv v v v v v v v v

Notes to Ta b le 1 – 1 :

(1) PLLs 5 and 6 each have eight single-ended outputs or four differential outputs.

(2) PLLs 11 and 12 each have one single-ended output.

(3) EP1S30 and EP1S40 devices do not support these PLLs in the 780-pin FineLine BGA

®

package.

S52001-3.2

Loading...

Loading...