Altera Corporation 4–9

June 2006 Stratix Device Handbook, Volume 2

Selectable I/O Standards in Stratix & Stratix GX Devices

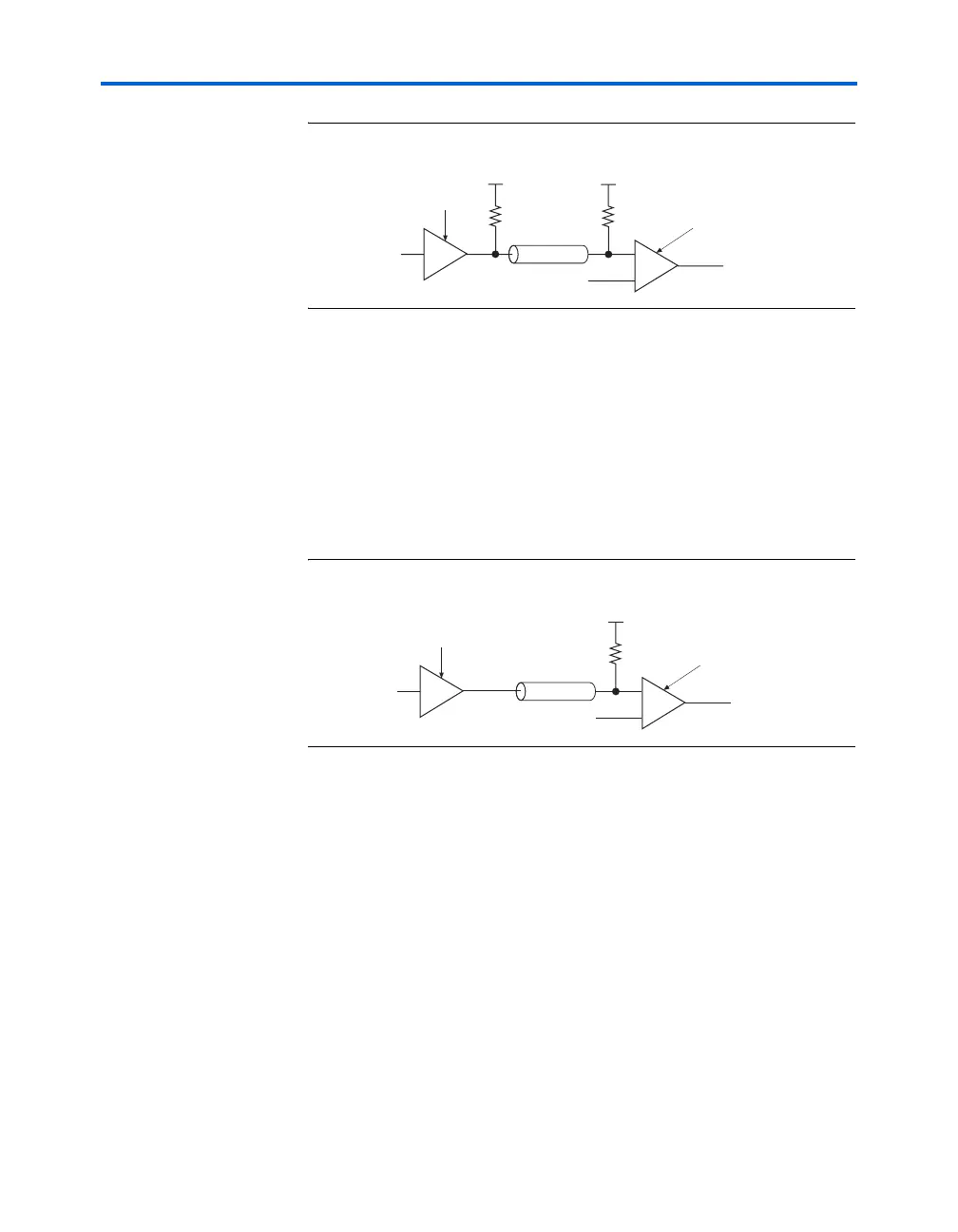

Figure 4–5. GTL+ Termination

CTT - EIA/JEDEC Standard JESD8-4

The CTT I/O standard is used for backplanes and memory bus interfaces.

The CTT standard defines the DC interface parameters for digital circuits

operating from 2.5- and 3.3-V power supplies. The CTT standard does not

require special circuitry to interface with LVTTL or LVCMOS devices

when the CTT driver is not terminated. The CTT standard requires a 1.5-V

V

REF

and a 1.5-V V

TT

(see Figure 4–6). Stratix and Stratix GX devices

support both input and output levels.

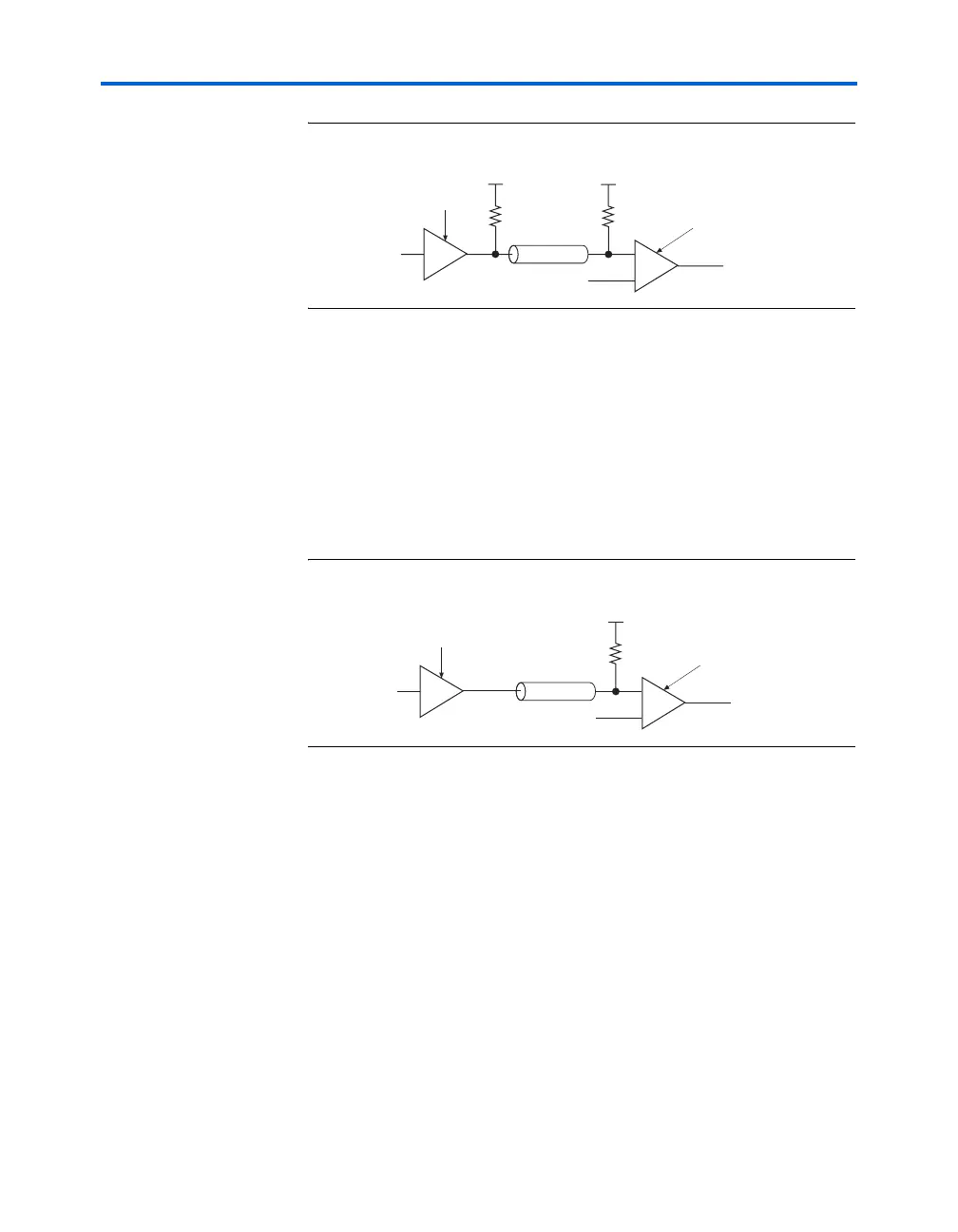

Figure 4–6. CTT Termination

SSTL-3 Class I & II - EIA/JEDEC Standard JESD8-8

The SSTL-3 I/O standard is a 3.3-V memory bus standard used for

applications such as high-speed SDRAM interfaces. This standard

defines the input and output specifications for devices that operate in the

SSTL-3 logic switching range of 0.0 to 3.3 V. The SSTL-3 standard specifies

an input voltage range of – 0.3 V ≤V

I

≤V

CCIO

+ 0.3 V. SSTL-3 requires a 1.5-

V V

REF

and a 1.5-V V

TT

to which the series and termination resistors are

connected (see Figures 4–7 and 4–8). Stratix and Stratix GX devices

support both input and output levels.

Output Buffer

Input Buffe

V

TT

= 1.5 V

50 Ω

Z = 50 Ω

V

REF

= 1.0 V

V

TT

= 1.5 V

50 Ω

Output Buffer

Input Buffer

V

TT

= 1.5 V

50 Ω

Z = 50 Ω

V

REF

= 1.5 V

Loading...

Loading...