Altera Corporation 4–11

June 2006 Stratix Device Handbook, Volume 2

Selectable I/O Standards in Stratix & Stratix GX Devices

Figure 4–10. SSTL-2 Class II Termination

SSTL-18 Class I & II - EIA/JEDEC Preliminary Standard JC42.3

The SSTL-18 I/O standard is a 1.8-V memory bus standard. This standard

is similar to SSTL-2 and defines input and output specifications for

devices that are designed to operate in the SSTL-18 logic switching range

0.0 to 1.8 V. SSTL-18 requires a 0.9-V V

REF

and a 0.9-V V

TT

to which the

series and termination resistors are connected. See Figures 4–11 and 4–12

for details on SSTL-18 Class I and II termination. Stratix and Stratix GX

devices support both input and output levels.

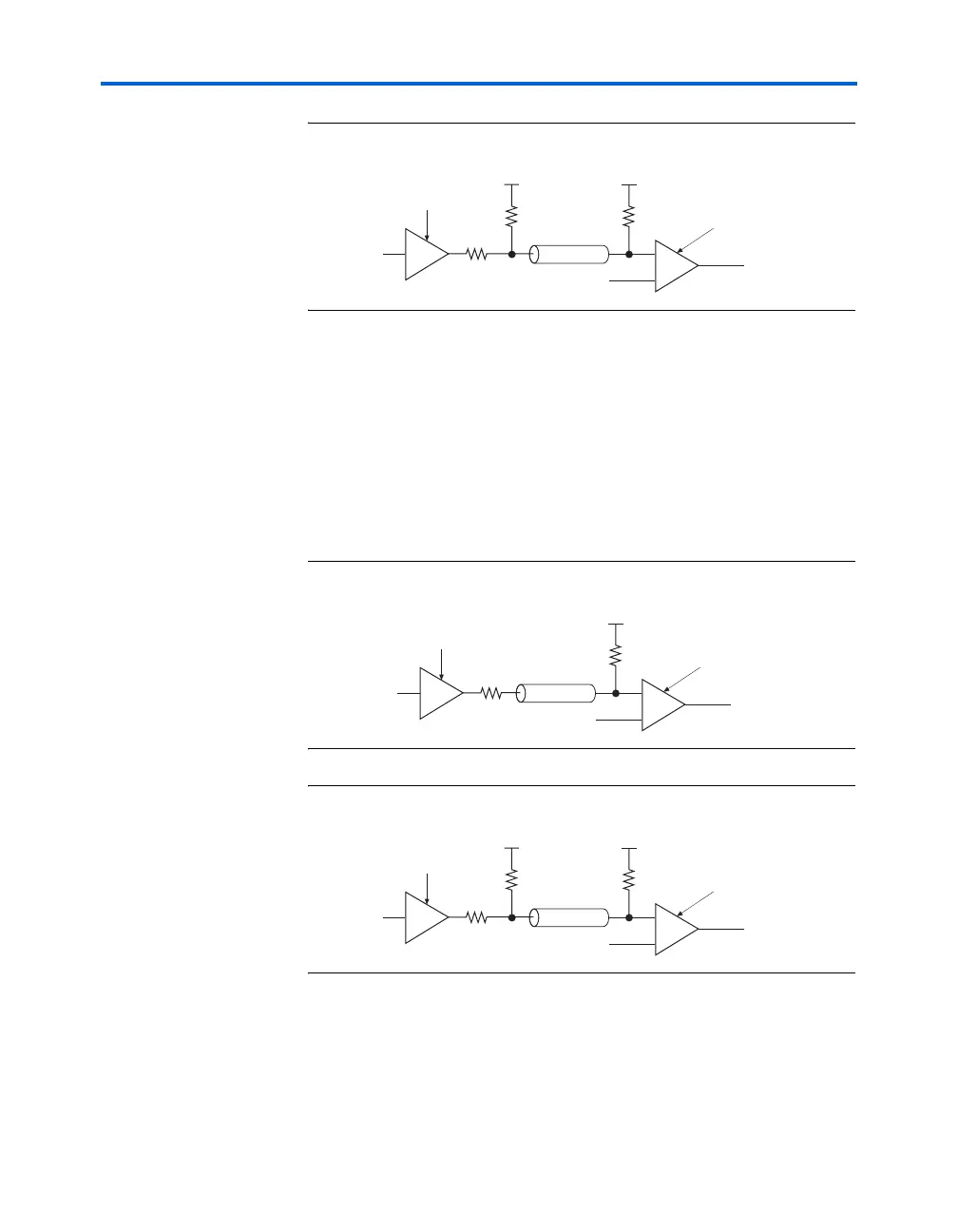

Figure 4–11. SSTL-18 Class I Termination

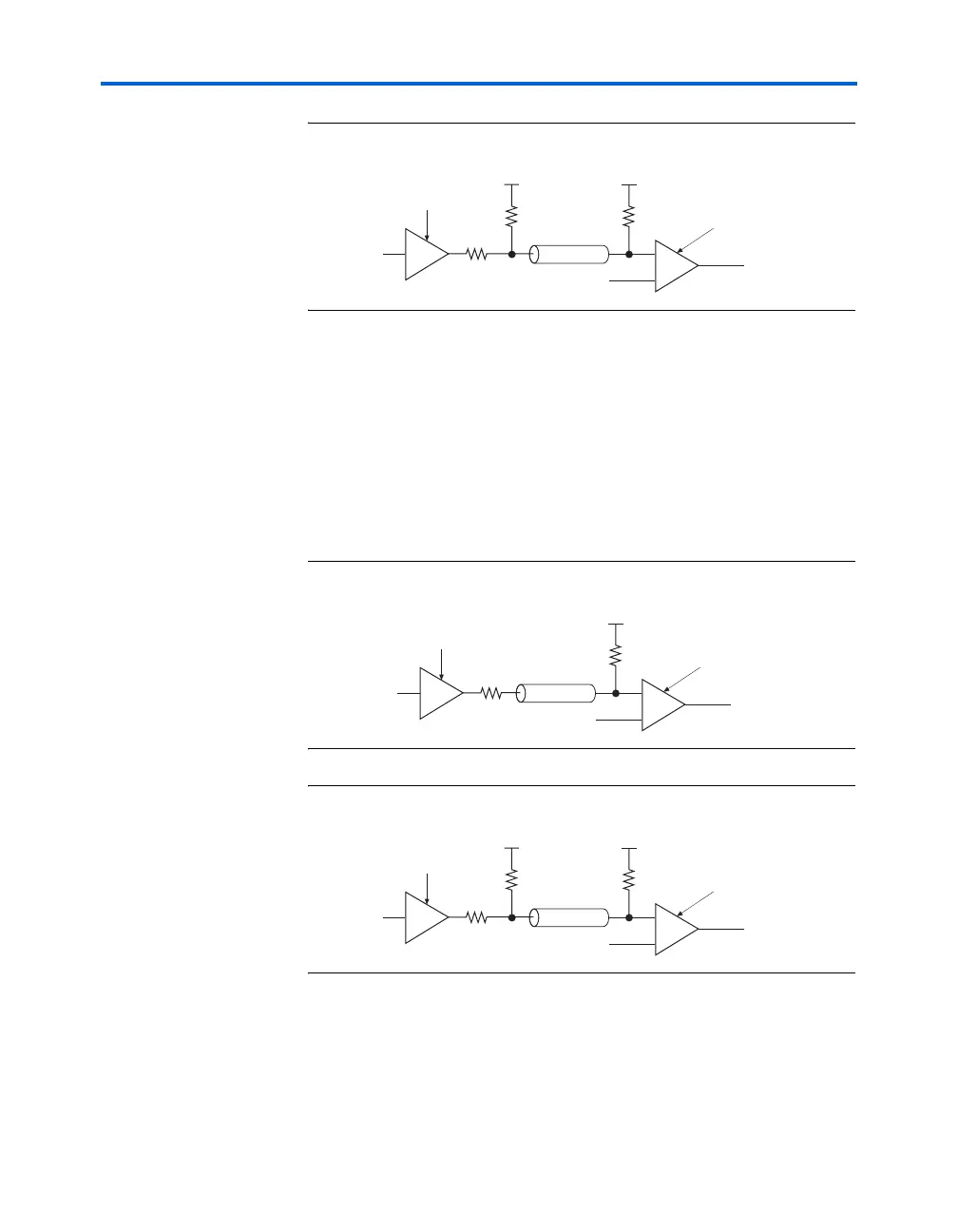

Figure 4–12. SSTL-18 Class II Termination

Differential SSTL-2 - EIA/JEDEC Standard JESD8-9A

The differential SSTL-2 I/O standard is a 2.5-V standard used for

applications such as high-speed DDR SDRAM clock interfaces. This

standard supports differential signals in systems using the SSTL-2

Output Buffer

Input Buffer

V

TT

= 1.25 V

50 Ω

V

TT

= 1.25 V

50 Ω

25 Ω

Z = 50 Ω

V

REF

= 1.25 V

Output Buffer

Input Buffer

V

TT

= 0.9 V

50 Ω

25 Ω

Z = 50 Ω

V

REF

= 0.9 V

Output Buffer

Input Buffer

V

TT

= 0.9 V

50 Ω

V

TT

= 0.9 V

50 Ω

25 Ω

Z = 50 Ω

V

REF

= 0.9 V

Loading...

Loading...