Altera Corporation 4–5

June 2006 Stratix Device Handbook, Volume 2

Selectable I/O Standards in Stratix & Stratix GX Devices

Stratix and Stratix GX devices support both input and output levels for

1.5-V LVCMOS operation.

1.5-V HSTL Class I & II - EIA/JEDEC Standard EIA/JESD8-6

The high-speed transceiver logic (HSTL) I/O standard is used for

applications designed to operate in the 0.0- to 1.5-V HSTL logic switching

range. This standard defines single ended input and output specifications

for all HSTL-compliant digital integrated circuits. The single ended input

standard specifies an input voltage range of – 0.3 V ≤V

I

≤V

CCIO

+ 0.3 V.

Stratix and Stratix GX devices support both input and output levels

specified by the 1.5-V HSTL I/O standard. The input clock is

implemented using dedicated differential input buffers. Two single-

ended output buffers are automatically programmed to have opposite

polarity so as to implement a differential output clock. Additionally, the

1.5-V HSTL I/O standard in Stratix and Stratix GX devices is compatible

with the 1.8-V HSTL I/O standard in APEX

TM

20KE and APEX 20KC

devices because the input and output voltage thresholds are compatible.

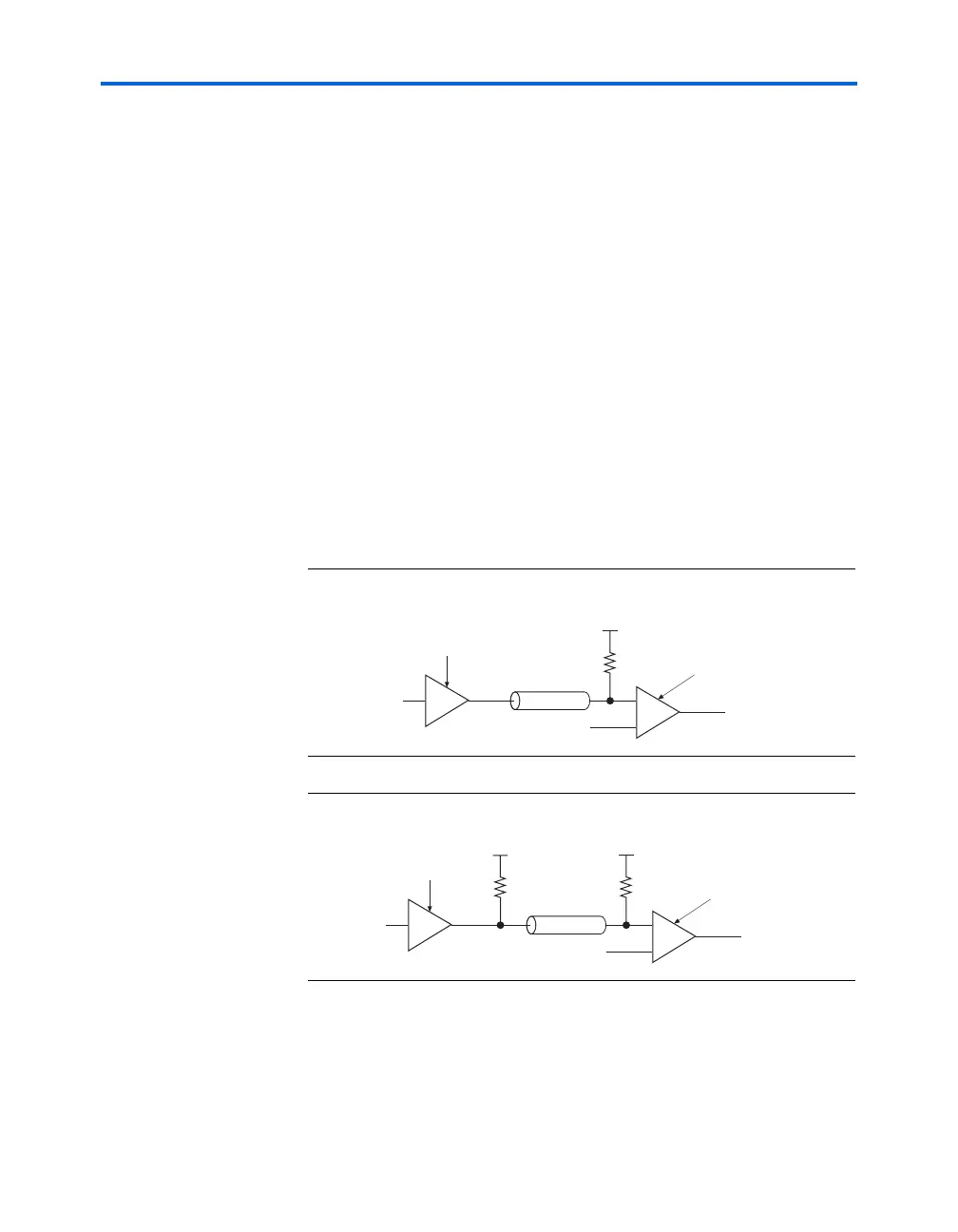

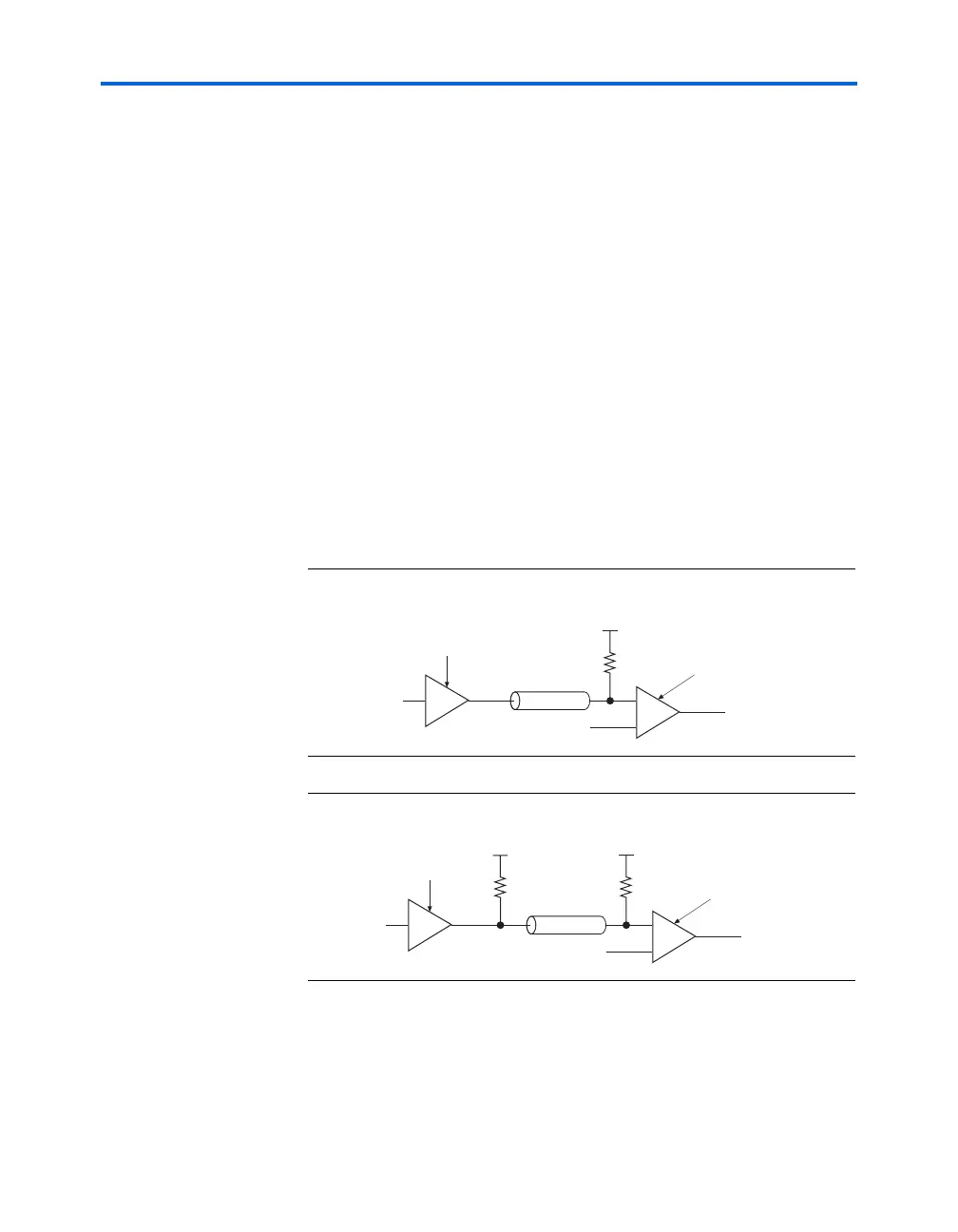

See Figures 4–1 and 4–2. Stratix and Stratix GX devices support both

input and output levels with V

REF

and V

TT

.

Figure 4–1. HSTL Class I Termination

Figure 4–2. HSTL Class II Termination

Output Buffer

Input Buffer

V

TT

= 0.75 V

50 Ω

Z = 50 Ω

V

REF

= 0.75 V

Output Buffer

Input Buffer

V

TT

= 0.75 V

50 Ω

V

TT

= 0.75 V

50 Ω

Z = 50 Ω

V

REF

= 0.75 V

Loading...

Loading...