8–24 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

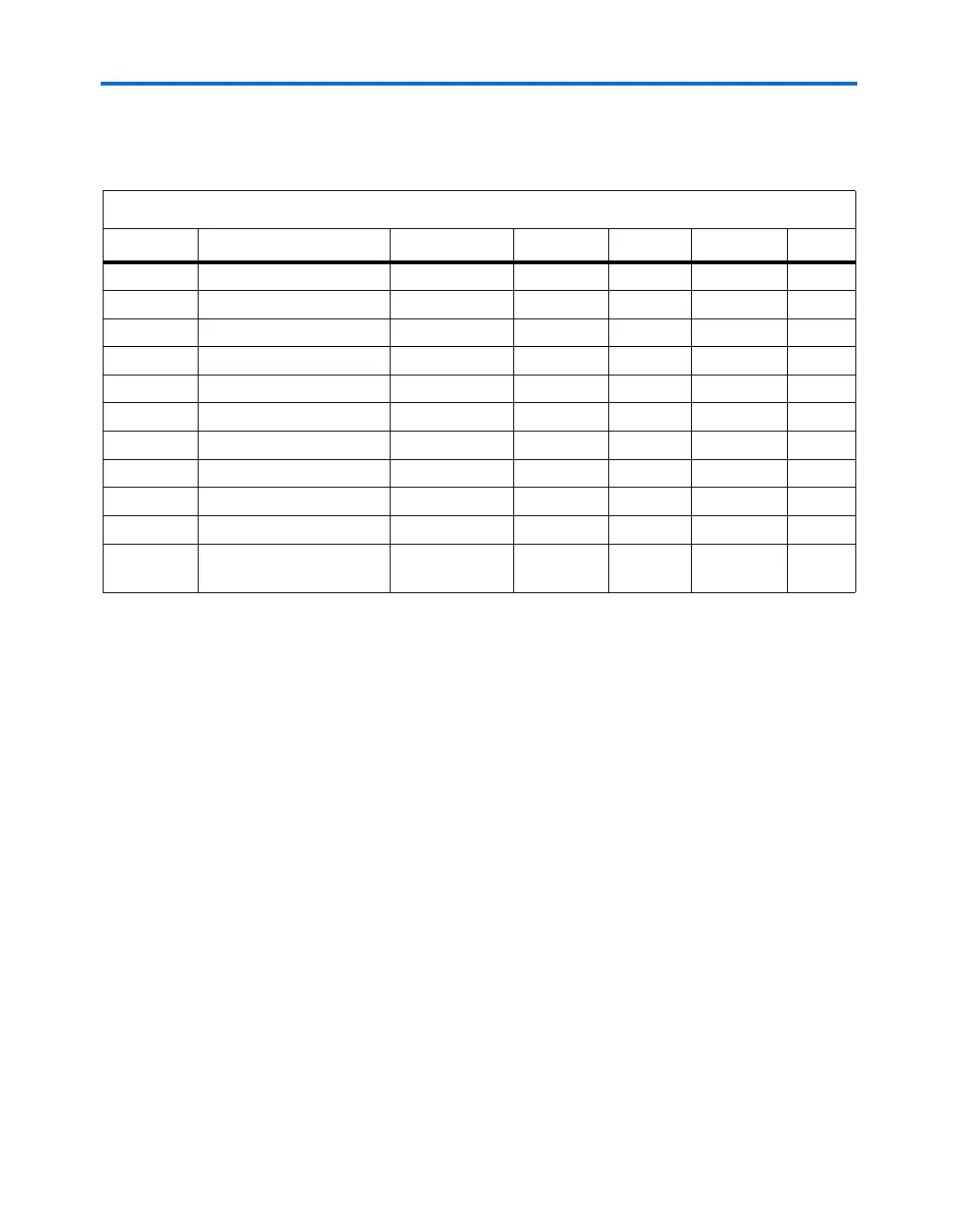

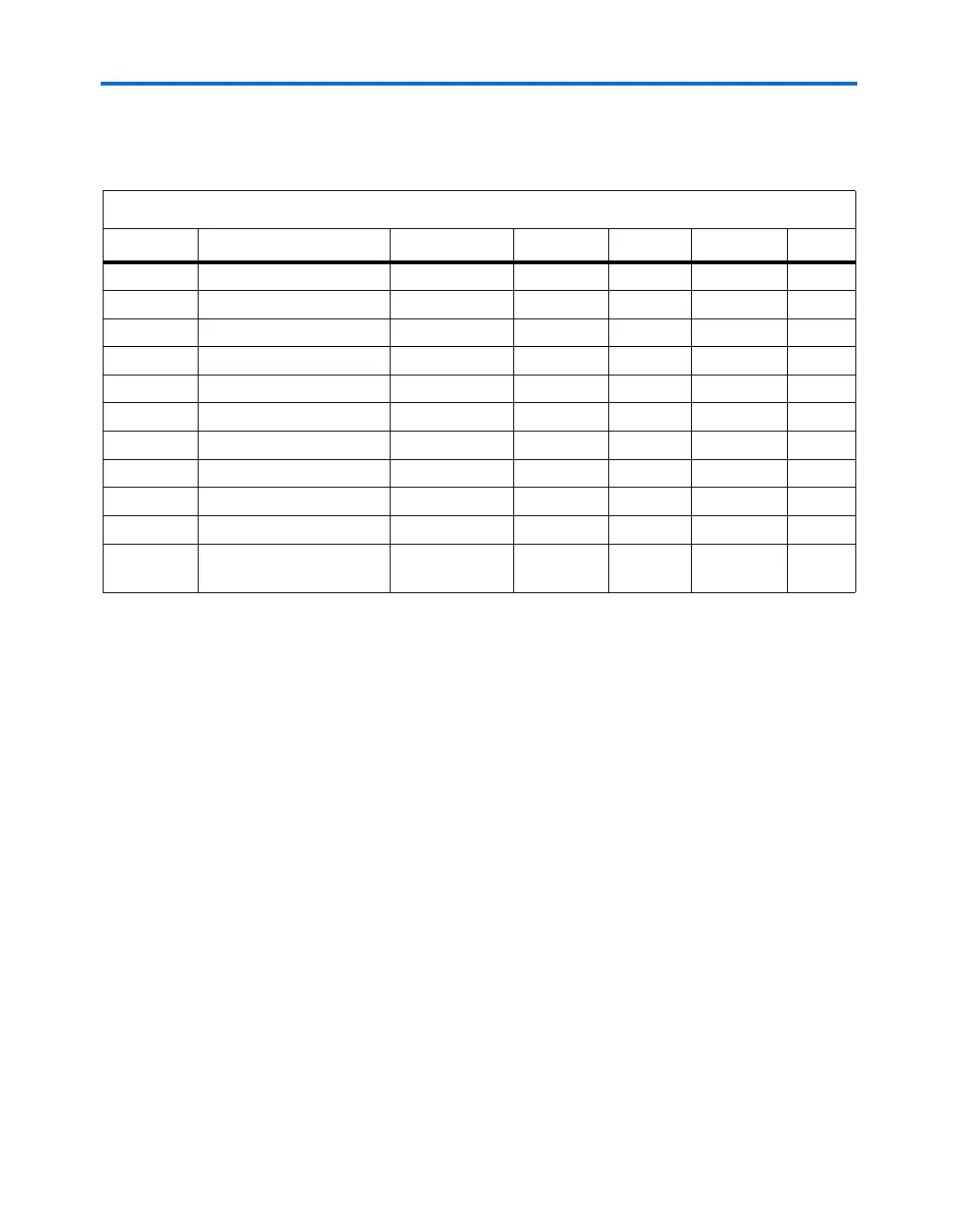

I/O Characteristics for XSBI, XGMII & XAUI

Table 8–11 lists the DC specifications for Stratix and Stratix GX devices

(1.5-V HSTL Class I).

10-Gigabit Ethernet MAC Core

As an Altera Megafunction Partners Program (AMPP

SM

) member,

MorethanIP provides a 10-Gigabit Ethernet MAC core for Altera

customers. MorethanIP’s 10-Gigabit Ethernet MAC core implements the

RS, the MAC layer, and user-programmable FIFO buffers for clock and

data decoupling.

Core Features

MorethanIP’s 10-Gigabit Ethernet MAC core provides the following

features:

■ Includes automatic pause frame generation (per IEEE 802.3 × 31) with

user-programmable pause quanta and pause-frame termination

■ Includes a programmable 48-bit MAC address with a promiscuous

mode option, and a programmable Ethernet frame length that

supports IEEE 802.1Q VLAN-tagged frames or jumbo Ethernet

frames

Table 8–11. DC Specifications for Stratix & Stratix GX Devices (1.5-V HSTL Class I) Note (1)

Symbol Parameter Conditions Minimum Typical Maximum Units

V

CCIO

I/O supply voltage 1.4 1.5 1.6 V

V

REF

Input reference voltage 0.68 0.75 0.9 V

V

TT

Termination voltage 0.7 0.75 0.8 V

V

IH

(DC) DC high-level input voltage V

REF

+ 0.1 V

V

IL

(DC) DC low-level input voltage –0.3 V

REF

– 0.1 V

V

IH

(AC) AC high-level input voltage V

REF

+ 0.2 V

V

IL

(AC) AC low-level input voltage V

REF

– 0.2 V

I

I

Input pin leakage current 0 < V

IN

< V

CCIO

–10 10 μA

V

OH

High-level output voltage I

OH

= –8 mA V

CCIO

– 0.4 V

V

OL

Low-level output voltage I

OL

= 8 mA 0.4 V

I

O

Output leakage current

(when output is high Z)

GND ≤ V

OUT

≤

V

CCIO

–10 10 μA

Note to Ta bl e 8 –11:

(1) Drive strength is programmable according to values shown in the Stratix Device Family Data Sheet section of the

Stratix Device Handbook, Volume 1 or the Stratix GX Device Family Data Sheet section of the Stratix GX Device

Handbook, Volume 1.

Loading...

Loading...