4–38 Altera Corporation

Stratix Device Handbook, Volume 2 June 2006

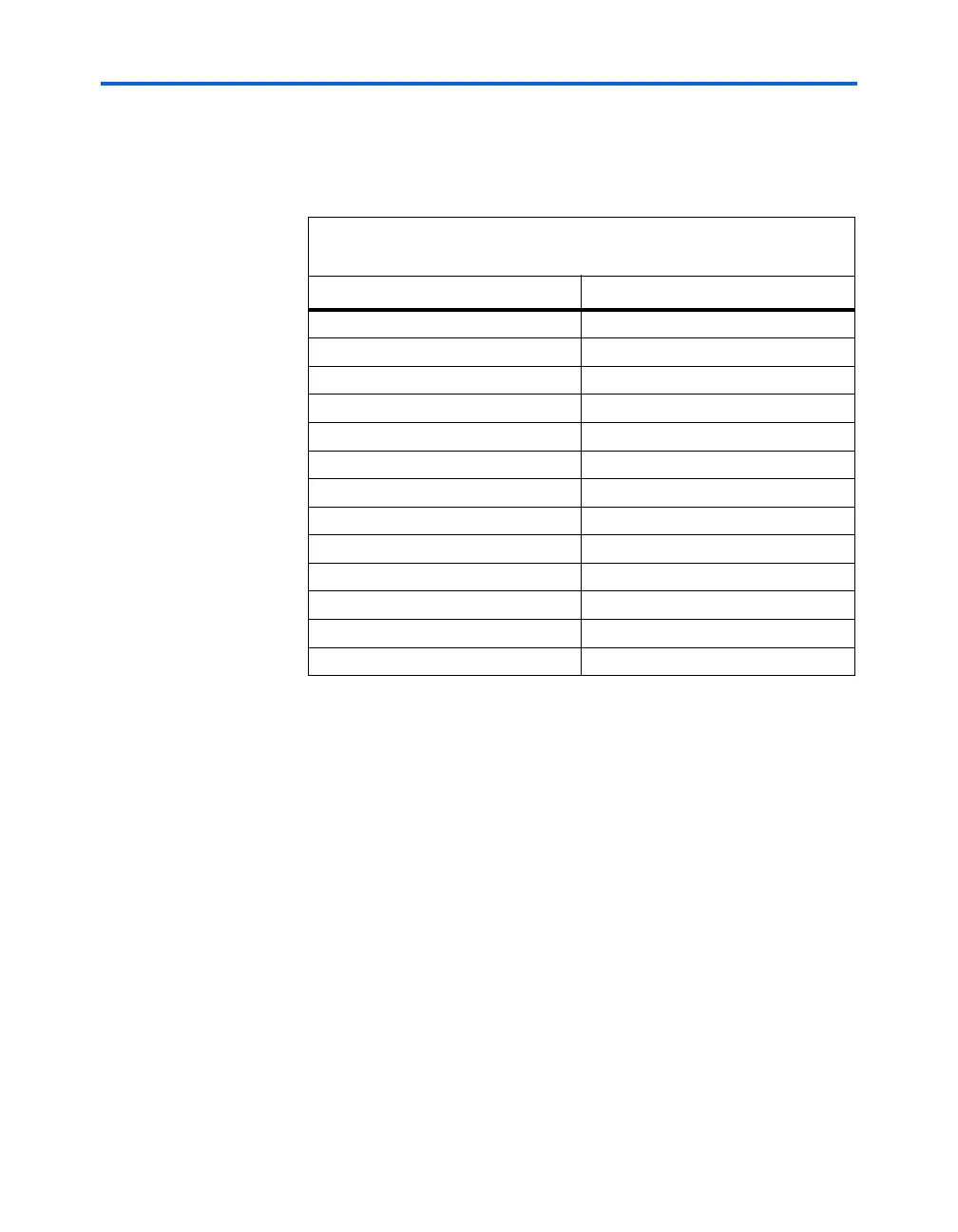

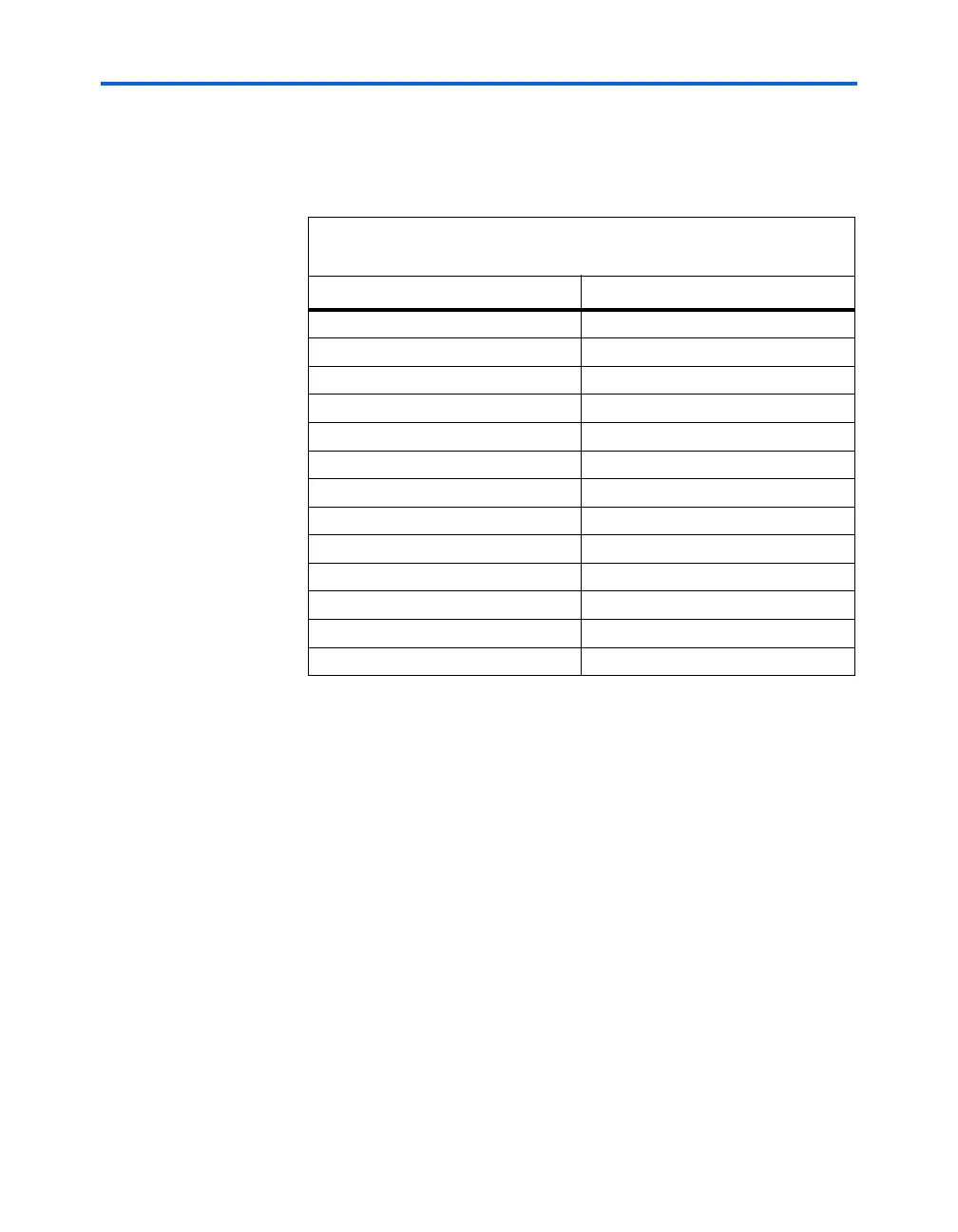

Power Source of Various I/O Standards

Power Source of

Various I/O

Standards

For Stratix and Stratix GX devices, the I/O standards are powered by

different power sources. To determine which source powers the input

buffers, see Table 4–13. All output buffers are powered by V

CCIO

.

Quartus II

Software

Support

You specify which programmable I/O standards to use for Stratix and

Stratix GX devices with the Quartus II software. This section describes

Quartus II implementation, placement, and assignment guidelines,

including

■ Compiler Settings

■ Device & Pin Options

■ Assign Pins

■ Programmable Drive Strength Settings

■ I/O Banks in the Floorplan View

■ Auto Placement & Verification

Compiler Settings

You make Compiler settings in the Compiler Settings dialog box

(Processing menu). Click the Chips & Devices tab to specify the device

family, specific device, package, pin count, and speed grade to use for

your design.

Table 4–13. The Relationships Between Various I/O Standards and the

Power Sources

I/O Standard Power Source

2.5V/3.3V LVTTL V

CCIO

PCI/PCI-X 1.0 V

CCIO

AGP V

CCIO

1.5V/1.8V V

CCIO

GTL V

CCINT

GTL+ V

CCINT

SSTL V

CCINT

HSTL V

CCINT

CTT V

CCINT

LVDS V

CCINT

LVPECL V

CCINT

PCML V

CCINT

HyperTransport V

CCINT

Loading...

Loading...