Altera Corporation 2–3

July 2005 Stratix Device Handbook, Volume 2

TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices

The extremely high memory bandwidth of the Stratix and Stratix GX

device families is a result of increased memory capacity and speed.

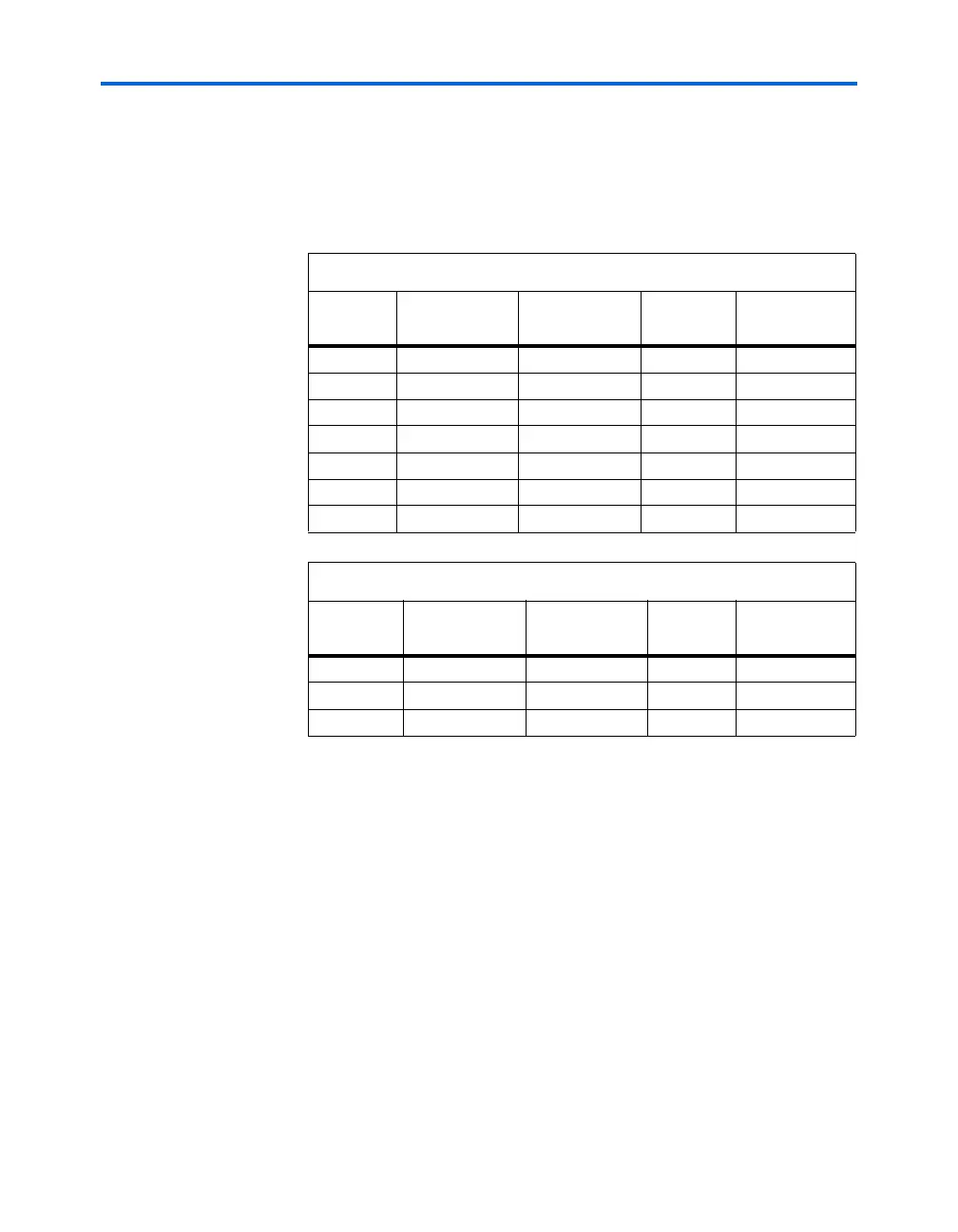

Table 2–2 shows the memory capacity for TriMatrix memory blocks in

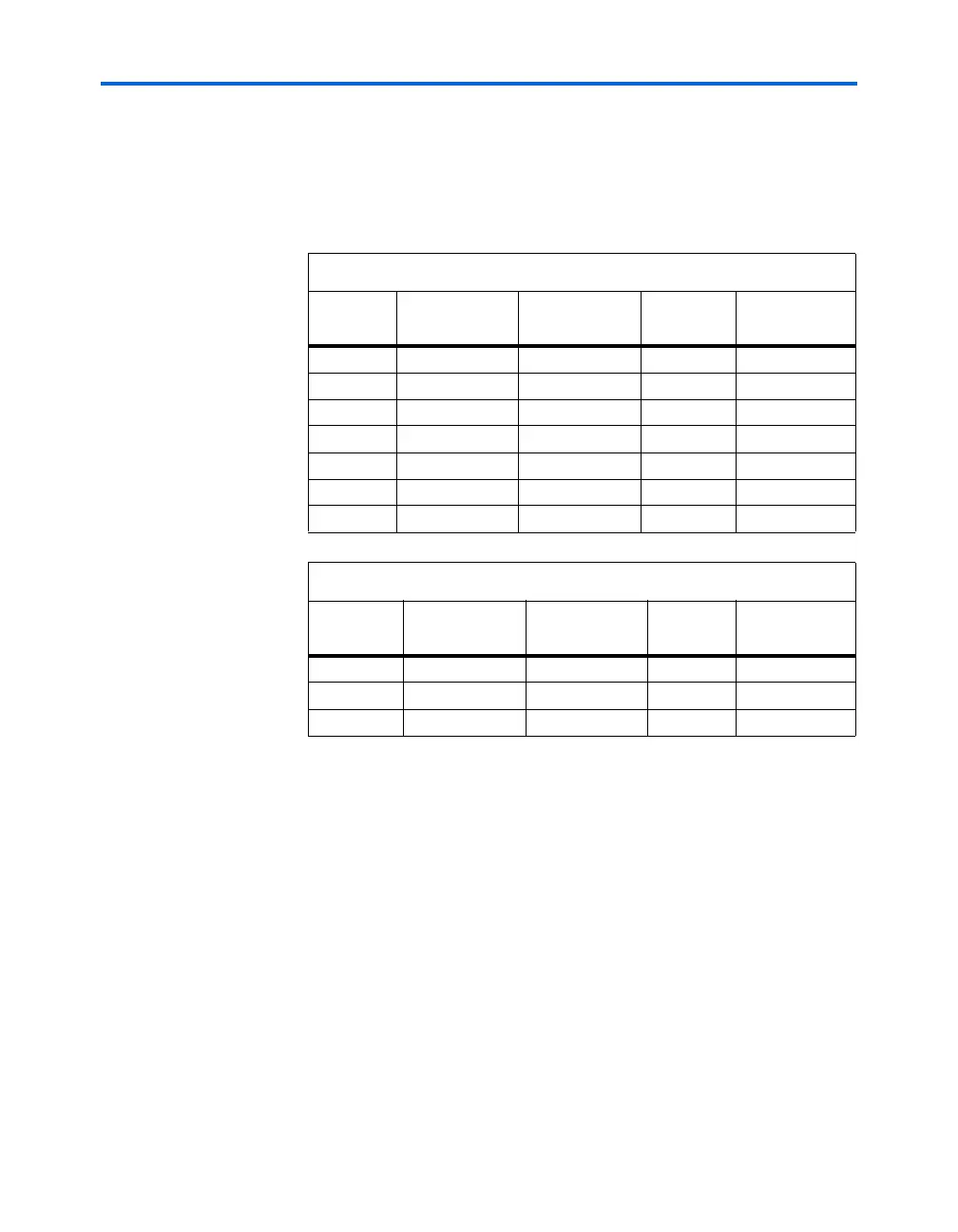

each Stratix device. Table 2–3 shows the memory capacity for TriMatrix

memory blocks in each Stratix GX device.

Clear Signals

When applied to input registers, the asynchronous clear signal for the

TriMatrix embedded memory immediately clears the input registers.

However, the output of the memory block does not show the effects until

the next clock edge. When applied to output registers, the asynchronous

clear signal clears the output registers and the effects are seen

immediately.

Parity Bit Support

The memory blocks support a parity bit for each byte. Parity bits are in

addition to the amount of memory in each RAM block. For example, the

M512 block has 576 bits, 64 of which are optionally used for parity bit

Table 2–2. TriMatrix Memory Distribution in Stratix Devices

Device

M512

Columns/Blocks

M4K

Columns/Blocks

M-RAM

Blocks

Total RAM Bits

EP1S10 4 / 94 2 / 60 1 920,448

EP1S20 6 / 194 2 / 82 2 1,669,248

EP1S25 6 / 224 3 / 138 2 1,944,576

EP1S30 7 / 295 3 / 171 4 3,317,184

EP1S40 8 / 384 3 / 183 4 3,423,744

EP1S60 10 / 574 4 / 292 6 5,215,104

EP1S80 11 / 767 4 / 364 9 7,427,520

Table 2–3. TriMatrix Memory Distribution in Stratix GX Devices

Device

M512

Columns/Blocks

M4K

Columns/Blocks

M-RAM

Blocks

Total RAM Bits

EP1SGX10 4 / 94 2 / 60 1 920,448

EP1SGX25 6 / 224 3 / 138 2 1,944,576

EP1SGX40 8 / 384 3 / 183 4 3,423,744

Loading...

Loading...