Altera Corporation Section I–1

Section I. Clock

Management

This section provides information on the different types of phase-lock

loops (PLLs). The feature-rich, enhanced PLLs assist you in managing

clocks internally and also have the ability to drive off-chip to control

system-level clock networks. The fast PLLs offer general-purpose clock

management with multiplication and phase shifting as well as

high-speed outputs to manage the high-speed differential I/O interfaces.

This chapter contains detailed information on the features, the

interconnections to the core and off-chip, and the specifications for both

types of PLLs.

This section contains the following:

■ Chapter 1, General-Purpose PLLs in Stratix & Stratix GX Devices

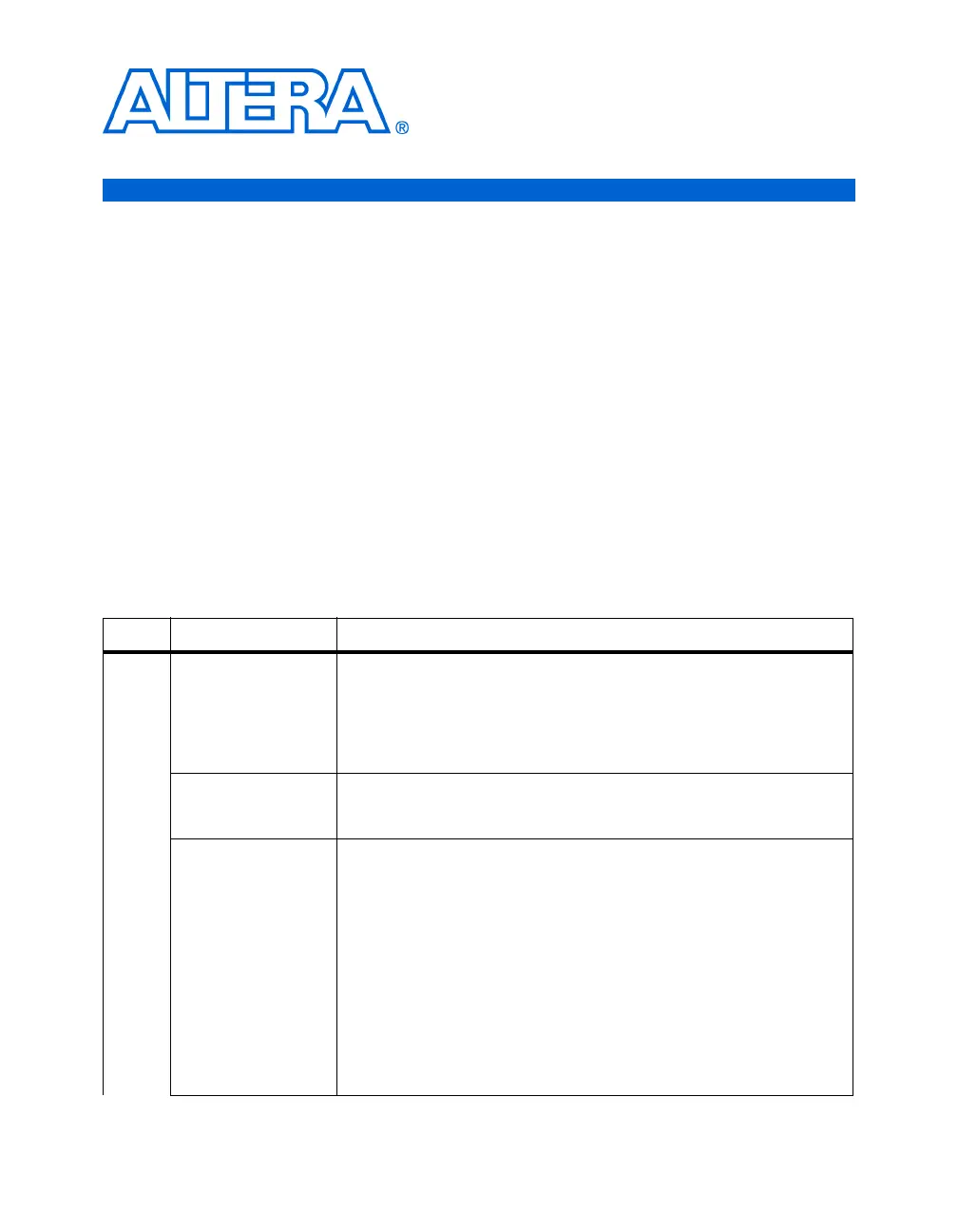

Revision History

The table below shows the revision history for Chapter 1.

Chapter Date/Version Changes Made

1 July 2005, v3.2 ● Removed information regarding delay shift (time delay elements).

● Updated Ta bl e 1 –8 .

● Updated “Clock Switchover” section.

● Updated Figure 1–22.

● Updated “Control Signals” section.

● Updated Table 1–16.

September 2004, v3.1

● Updated Note 1 in Table 1–17 on page 1–32.

● Updated Note 1 in Table 1–21 on page 1–48.

● Updated Table 1–12 on page 1–34.

April 2004, v3.0

● Changed PCI-X to PCI-X 1.0 throughout volume.

● Note 3 added to columns 11 and 12 in Table 1–1.

● Deleted “Stratix GX Clock Input Sources for Enhanced and Fast PLLs”

table.

● Deleted “Stratix GX Global and Regional Clock Output Line Sharing for

Enhanced and Fast PLLS” table.

● Deleted “Stratix GX CLK and FPLLCLK Input Pin Connections to Global

& Regional Clock Networks” table.

● Changed CLK checkmarks in Table 1–14.

● Updated notes to Table 1–3. and Figure 1–3.

● Added Table 1–7.

● Clock Switchover section has been moved to AN 313.

● Changed RCLK values in Figures 1–20 and 1–22.

Loading...

Loading...