1–32 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Fast PLLs

general purpose abilities of the Fast PLL. For information on the high-

speed differential I/O interface capabilities, see the High-Speed Differential

I/O Interfaces in Stratix Devices chapter.

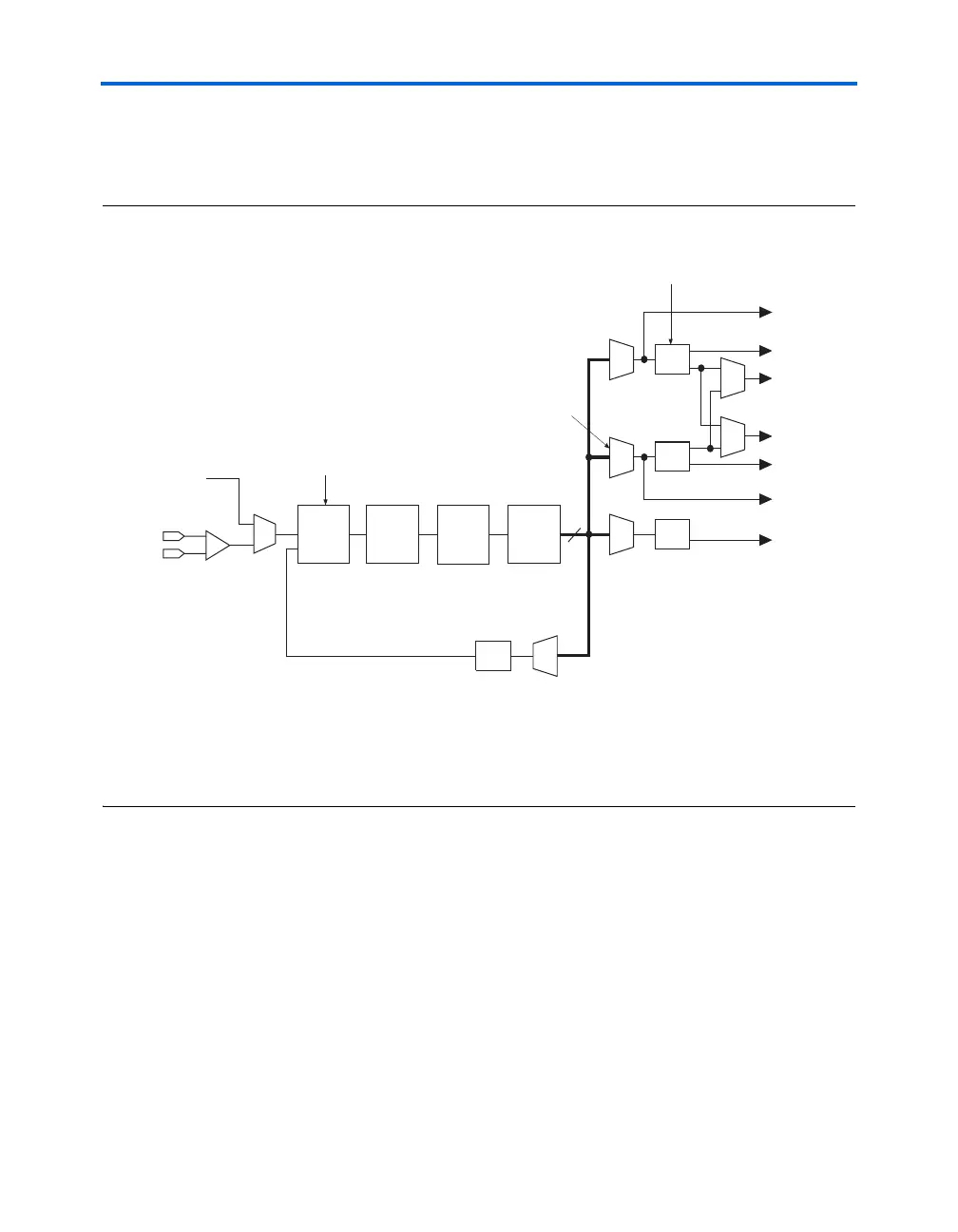

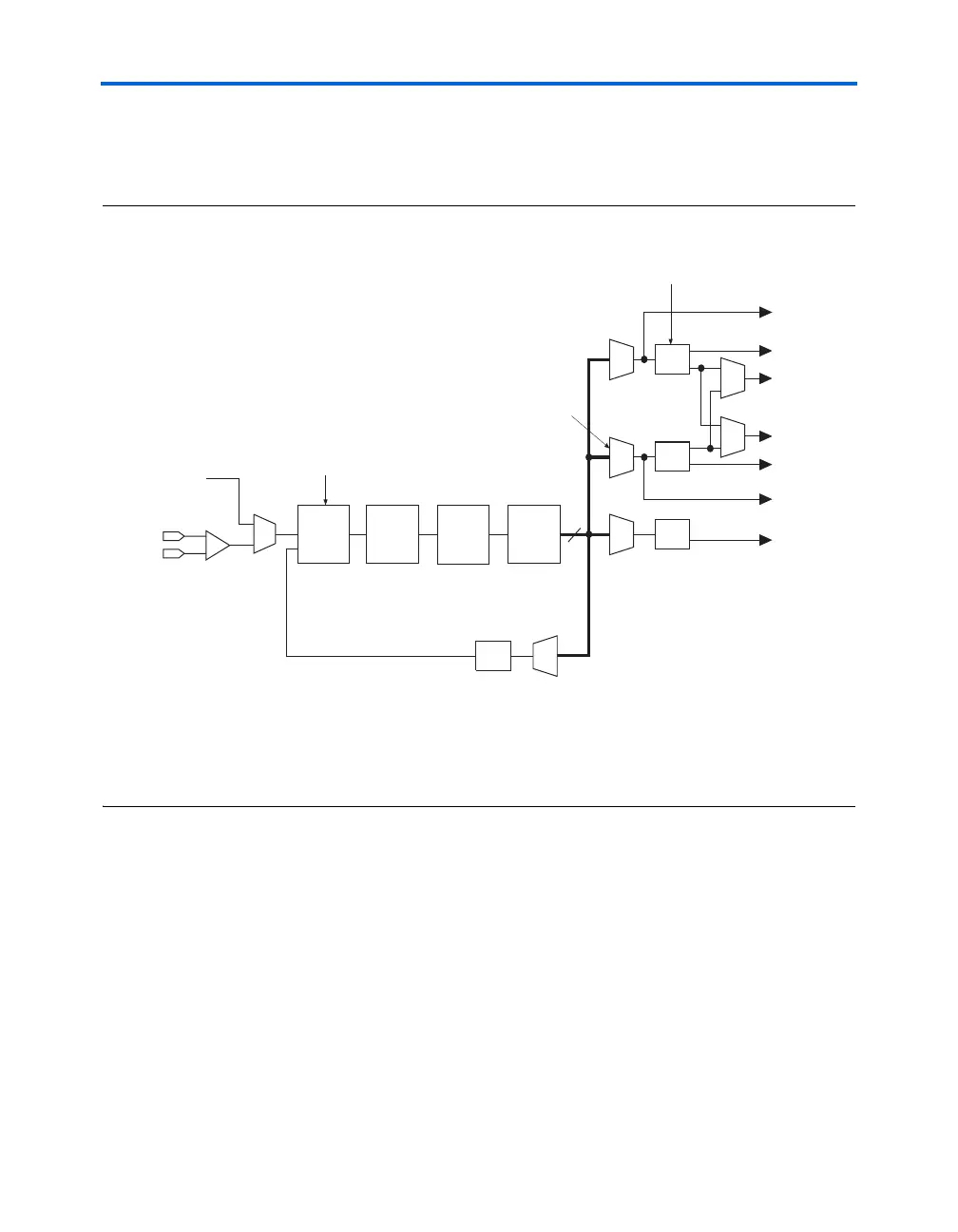

Figure 1–17. Stratix & Stratix GX Fast PLL Block Diagram

Notes to Figure 1–17:

(1) The global or regional clock input can be driven by an output from another PLL or any dedicated CLK or FCLK pin.

It cannot be driven by internally-generated global signals.

(2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES. Stratix and Stratix GX

devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

(3) This signal is a high-speed differential I/O support SERDES control signal.

Charge

Pump

VCO

÷g0

8

Clock

Input

PFD

÷l1

÷l0

÷m

Loop

Filter

Phase

Frequency

Detector

VCO Phase Selection

Selectable at each PLL

Output Port

Post-Scale

Counters

Global or

regional clock

Global or

regional clock

Global or

regional clock

diffioclk2 (2)

diffioclk1 (2)

txload_en (3)

rxload_en (3)

Global or

regional clock

(1)

Loading...

Loading...