9–12 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Introduction

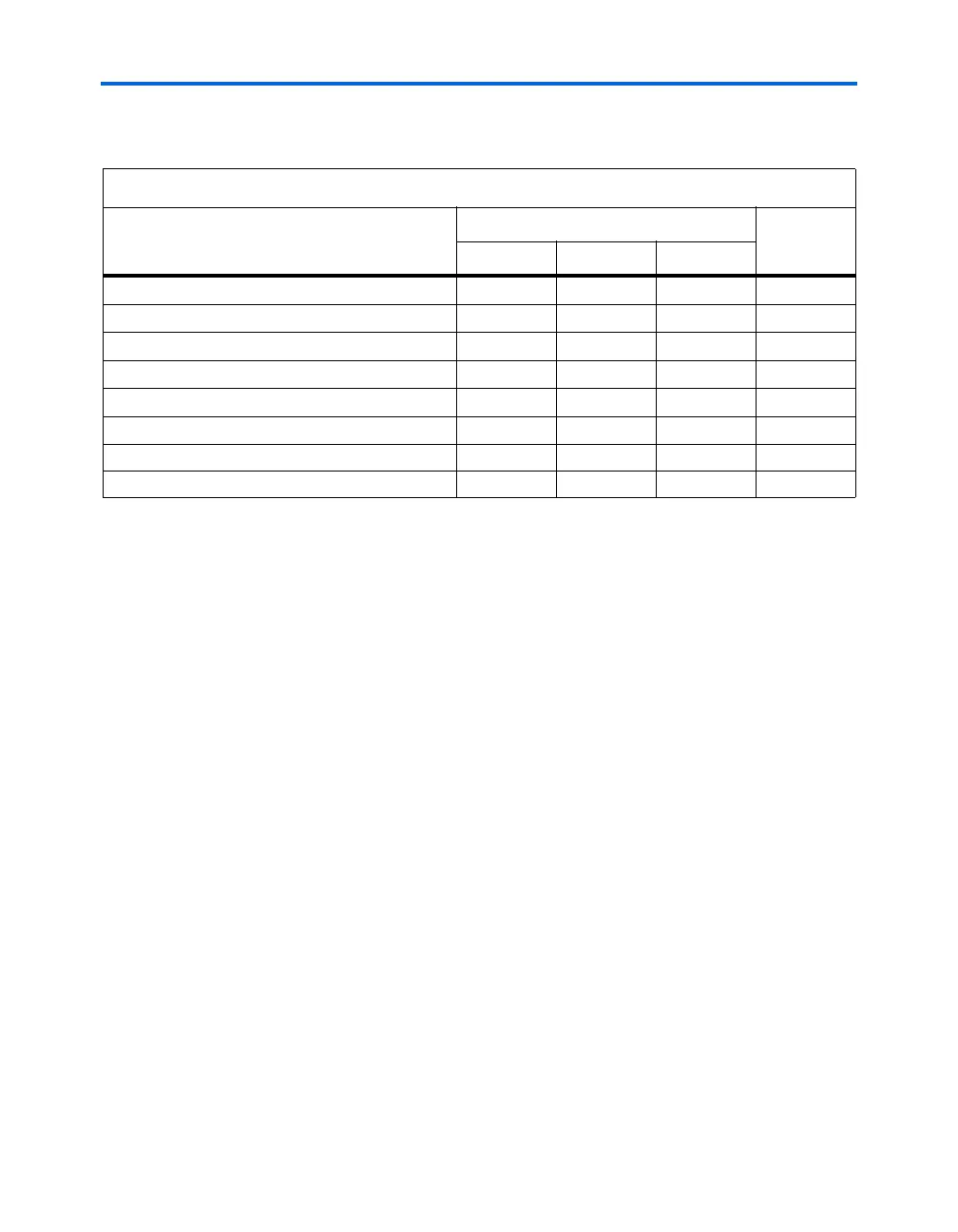

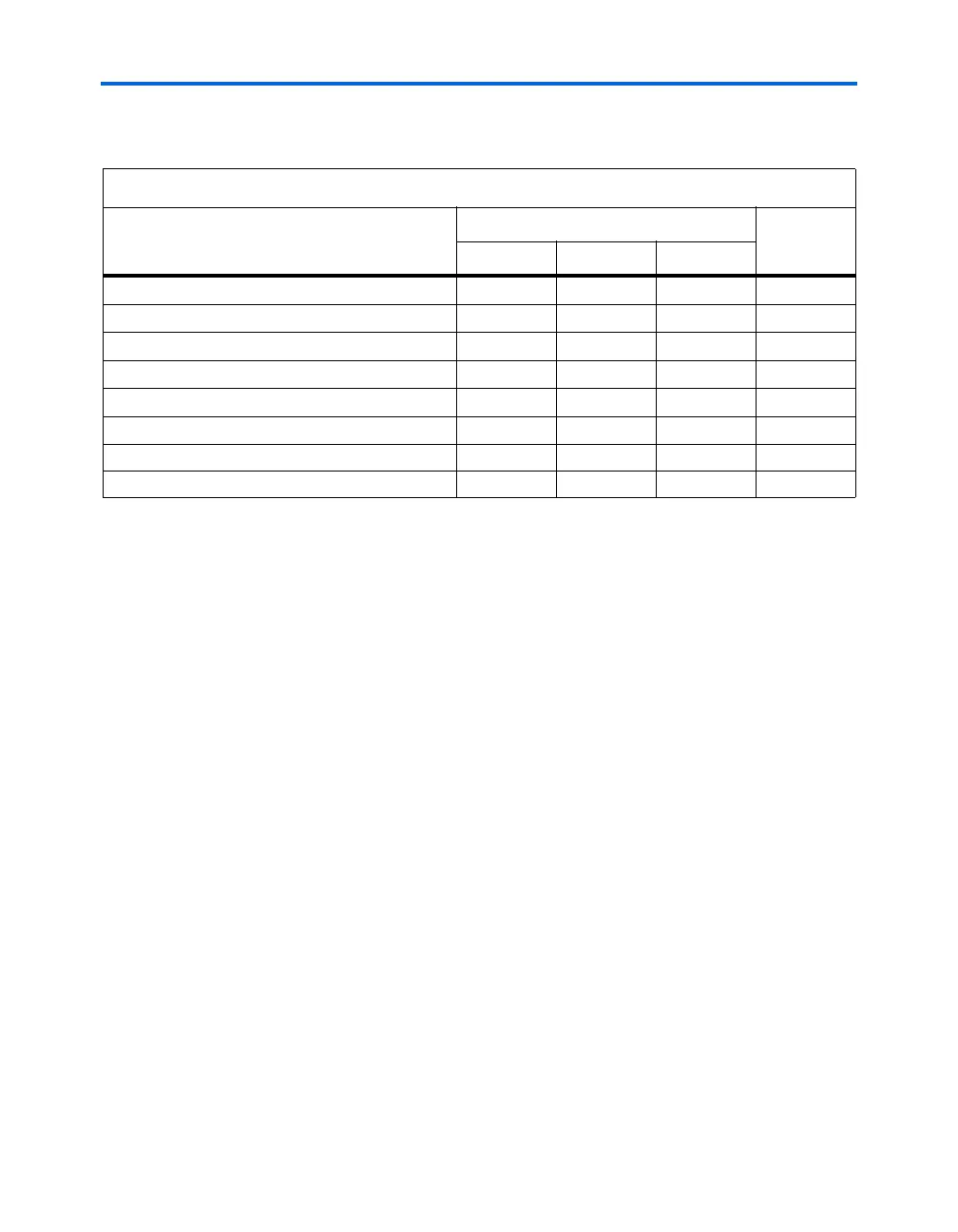

Table 9–6 lists the timing specifications for the SFI-4 framer receiver.

Electrical Specifications

SFI-4 uses LVDS as a high-speed data transfer mechanism to implement

the SFI-4 interface. Table 9–7 lists the DC electrical characteristics for the

interface, which are based on the IEEE Std. 1596.3-1996 7 specification.

For more information on the voltage specification of LVDS I/O standards

in Stratix and Stratix GX devices, see the Stratix Device Family Data Sheet

section of the Stratix Device Handbook, Volume 1 and the High-Speed

Differential I/O Interfaces in Stratix Devices chapter or the Stratix GX Device

Family Data Sheet section of the Stratix GX Device Handbook, Volume 1 and

the High-Speed Differential I/O Interfaces in Stratix Devices chapter.

Table 9–6. Framer Receiver Timing Specifications

Parameter

Value

Unit

Min Typ Max

RX_CLK (T

period

)

1,608 ps

Data invalid window before the rising edge (T

cq_pre

)200ps

Data invalid window after the rising edge (T

cq_post

)200ps

RX_CLK duty cycle

45 55 %

Data set-up time (T

setup

) 300 ps

Data hold time (T

hold

) 300 ps

Framer sampling window 600 ps

Receiver skew margin (RSKM) 304 ps

Loading...

Loading...