Altera Corporation Section II–1

Section II. Memory

This section provides information on the TriMatrix

™

Embedded Memory

blocks internal to Stratix

®

devices and the supported external memory

interfaces.

It contains the following chapters:

■ Chapter 2, TriMatrix Embedded Memory Blocks in

Stratix & Stratix GX Devices

■ Chapter 3, External Memory Interfaces in Stratix & Stratix GX

Devices

The QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices

chapter is removed in this version of the Stratix Device Handbook. The

information is available in AN 349: Interfacing QDR SRAM with Stratix and

Stratix GX Devices.

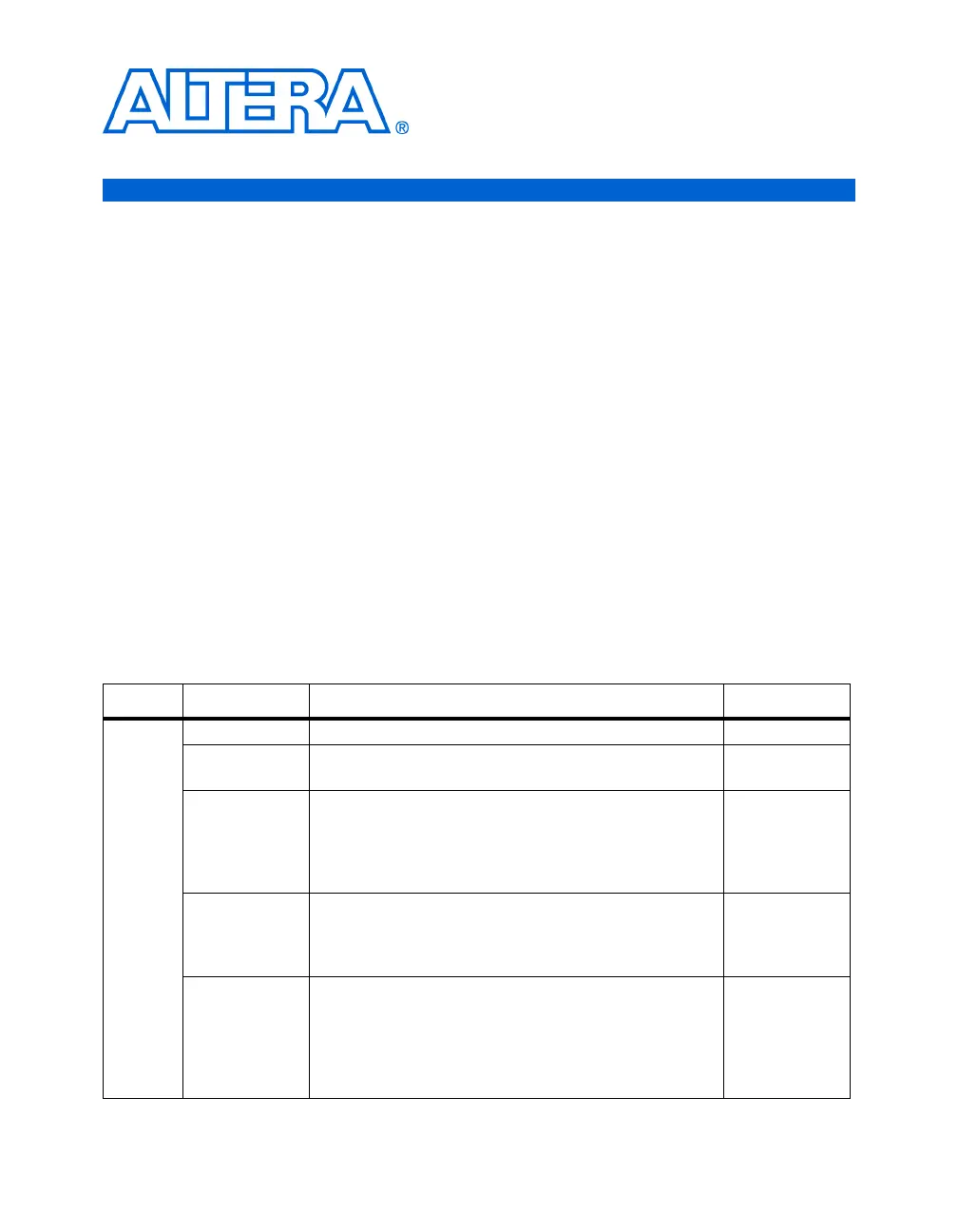

Revision History

The table below shows the revision history for Chapters 2 and 3.

Chapter Date/Version Changes Made Comments

2 July 2005, v3.3 ● Updated “Implementing True Dual-Port Mode” section.

January 2005,

v3.2

● Minor technical content update.

September

2004, v3.1

● Updated Note 1 in Figure 2–12 on page 2–22.

● Updated description about using two different clocks in a

dual-port RAM on page 2–27.

● Deleted description of M-RAM block and document

references on page 2–27.

April 2004, v3.0

● Synchronous occurrences are renamed to pipelined.

● Pseudo-synchronous occurrences are renamed flow-

through.

● Added AND gate to Figure 2–12.

July 2003, v2.0

● Updated performance specification for TriMatrix memory

in Table 2-1.

● Added addressing example for a RAM that is using

mixed-width mode, page 2-9.

● Added Note 1 to Tables 2-9 and 2-10, Note 3 to Figure 2-

11, and Note 2 to Figures 2-12 and 2-13.

Loading...

Loading...