Altera Corporation 8–13

July 2005 Stratix Device Handbook, Volume 2

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

XGMII

The purpose of XGMII is to provide a simple, inexpensive, and easy to

implement interconnection between the MAC sublayer and the PHY.

Though XGMII is an optional interface, it is used extensively in the

10-Gigabit Ethernet standard as the basis for the specification. The

conversion between the parallel data paths of XGMII and the serial MAC

data stream is carried out by the reconciliation sublayer. The

reconciliation sublayer maps the signal set provided at the XGMII to the

physical layer signaling (PLS) service primitives provided at the MAC.

XGMII supports a 10-Gbps MAC data rate.

Functional Description

The XGMII is composed of independent transmit and receive paths. Each

direction uses 32 data signals, TXD[31..0] and RXD[31..0], 4 control

signals, TXC[3..0] and RXC[3..0], and a clock TX_CLK and RX_CLK.

Figure 8–10 shows the XGMII functional block diagram.

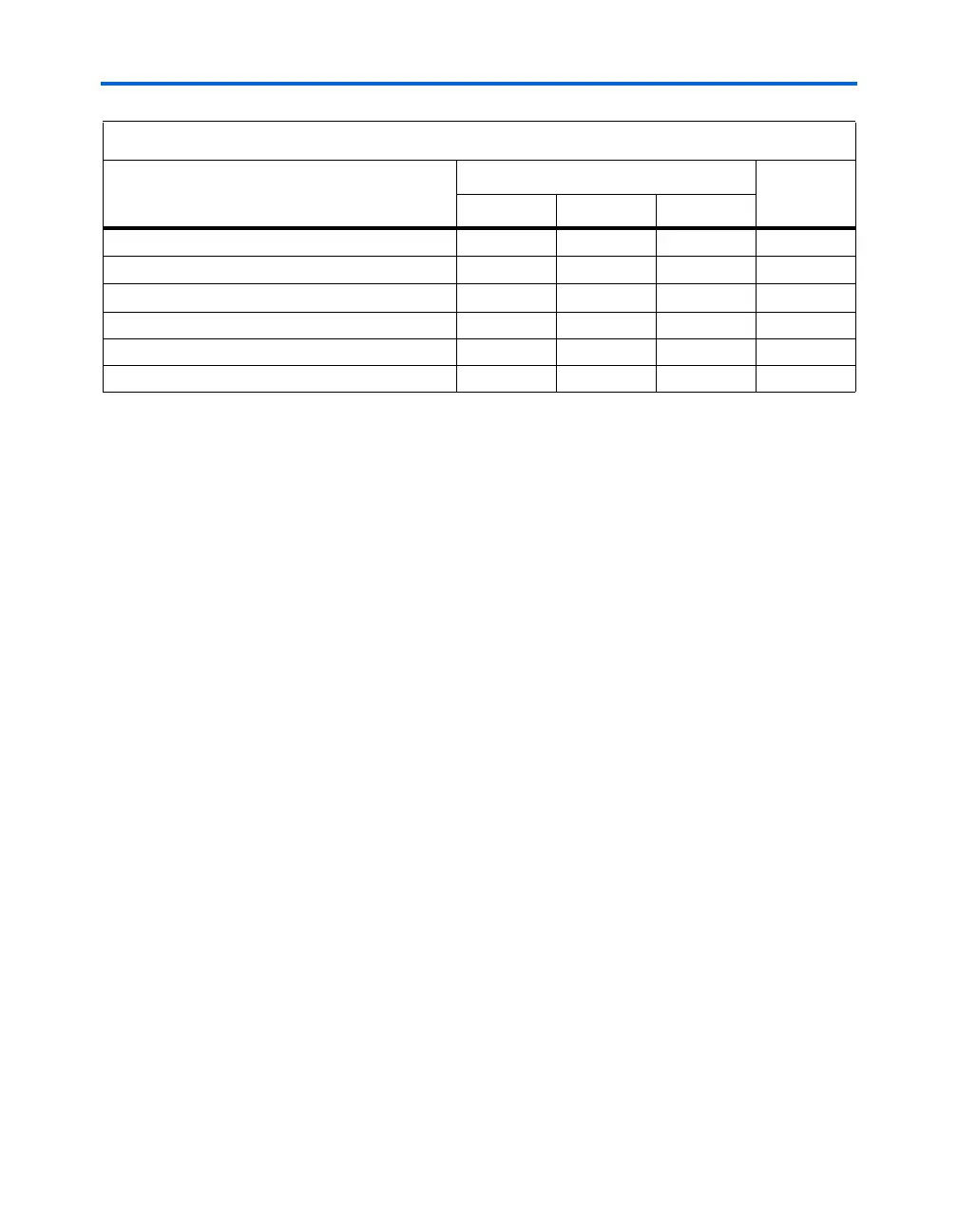

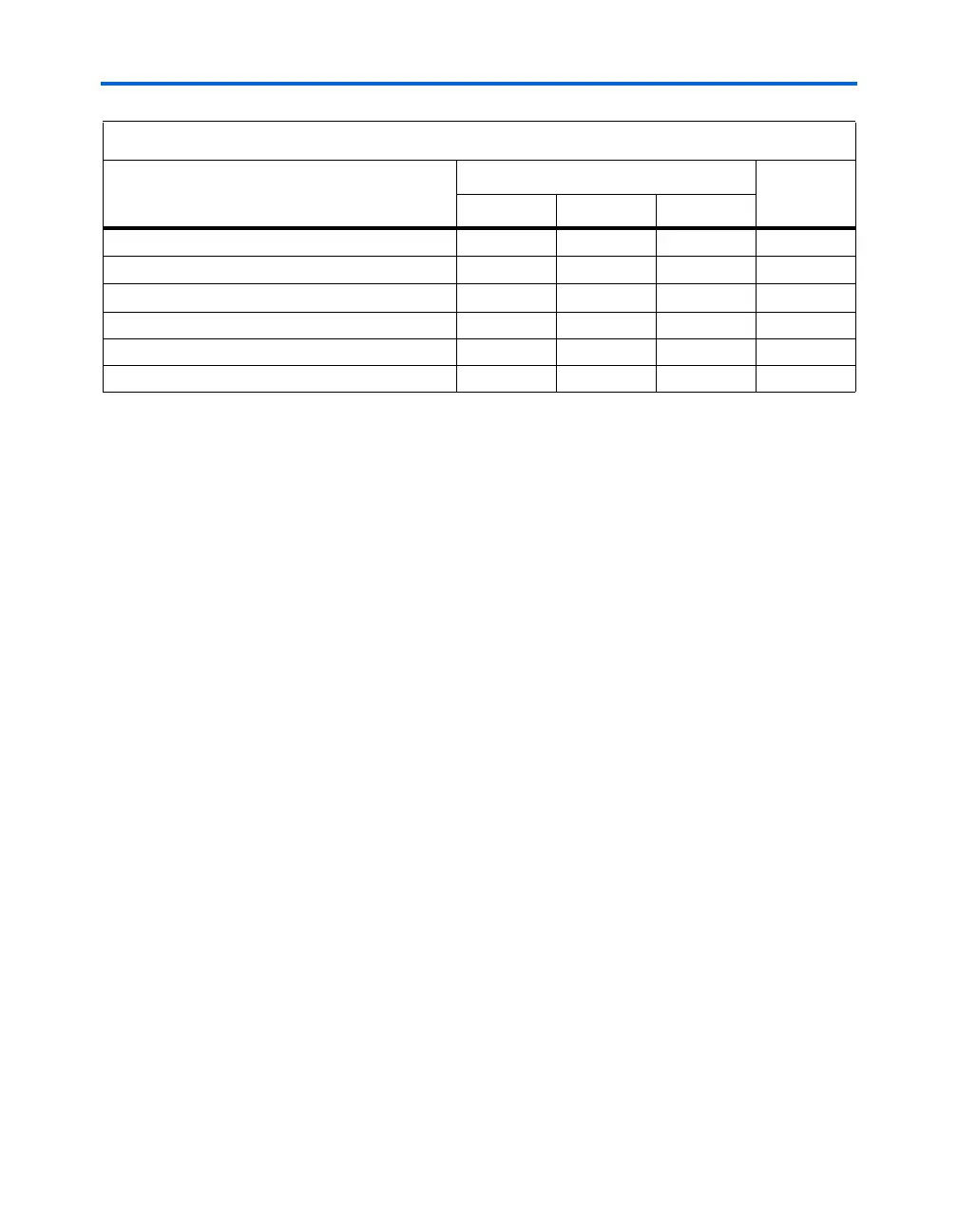

PMA_RX_CLK duty cycle

45 55 %

Data set-up time (T

setup

) 300 ps

Data hold time (T

hold

) 300 ps

PCS sampling window 600 ps

RSKM (WAN) 304 ps

RSKM (LAN) 276 ps

Table 8–5. PCS Receiver Timing Specifications (Part 2 of 2)

Parameter

Value

Unit

Min Typ Max

Loading...

Loading...