5–20 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Differential I/O Interface & Fast PLLs

Fast PLL Specifications

You can drive the fast PLLs by an external pin or any one of the sectional

clocks [21..0]. You can connect the clock input directly to local or global

clock lines, as shown in Figure 5–14. You cannot use the sectional-clock

inputs to the fast PLL’s input multiplexer for the receiver PLL. You can

only use the sectional clock inputs in the transmitter only mode or as a

general purpose PLL.

DIFFIOCLK14

v

DIFFIOCLK15

v

DIFFIOCLK16

v

Notes to Ta b le 5 – 4 :

(1) PLLs 5, 6, 11, and 12 are not fast PLLs.

(2) The input clock for PLLs used to clock receiver the rx_inclock port on the altlvds_rx megafunction must be

driven by a dedicated clock pin (CLK[3..0] and CLK[8..11]) or the corner pins that clock the corner PLLs

(FPLL[10..7]CLK).

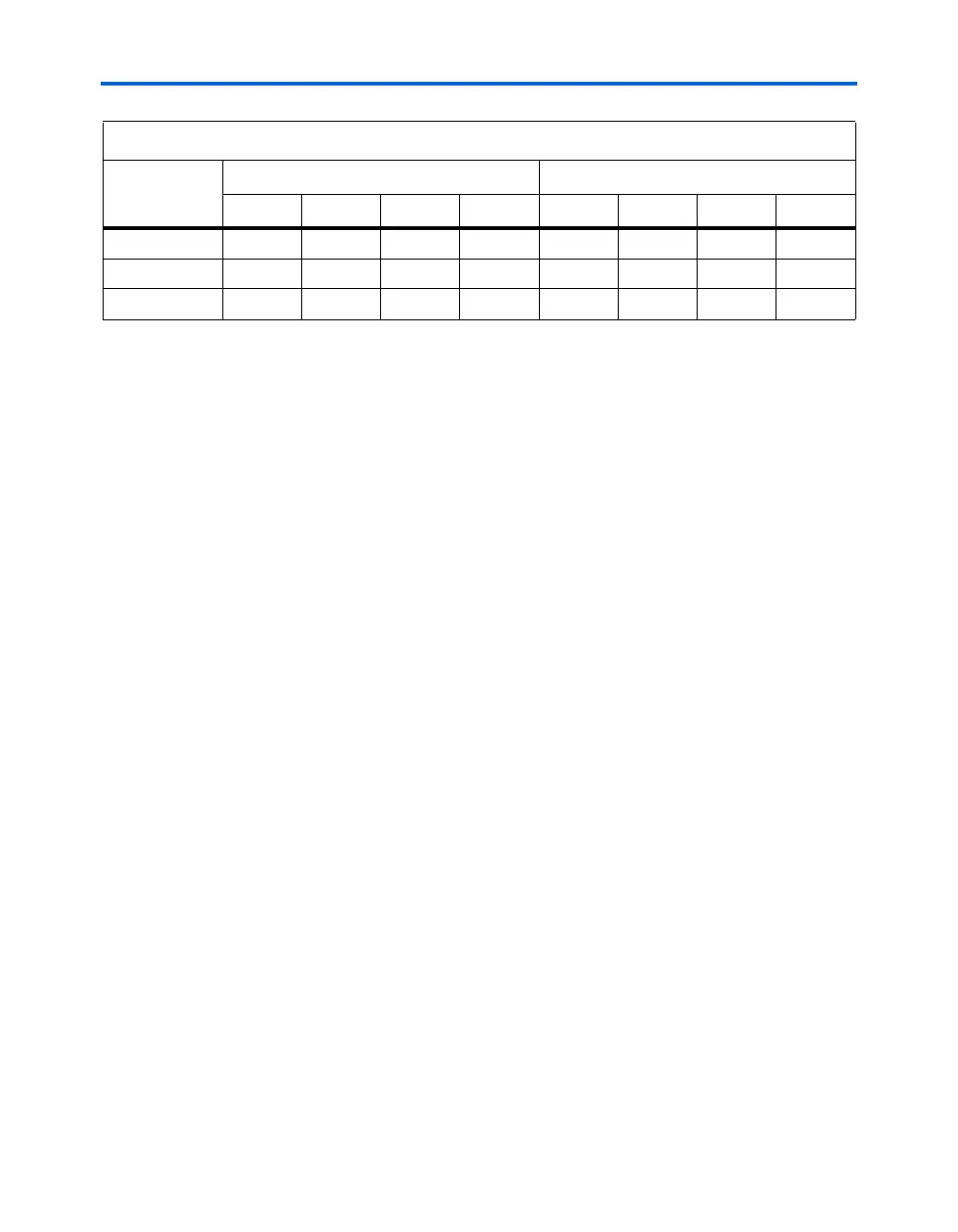

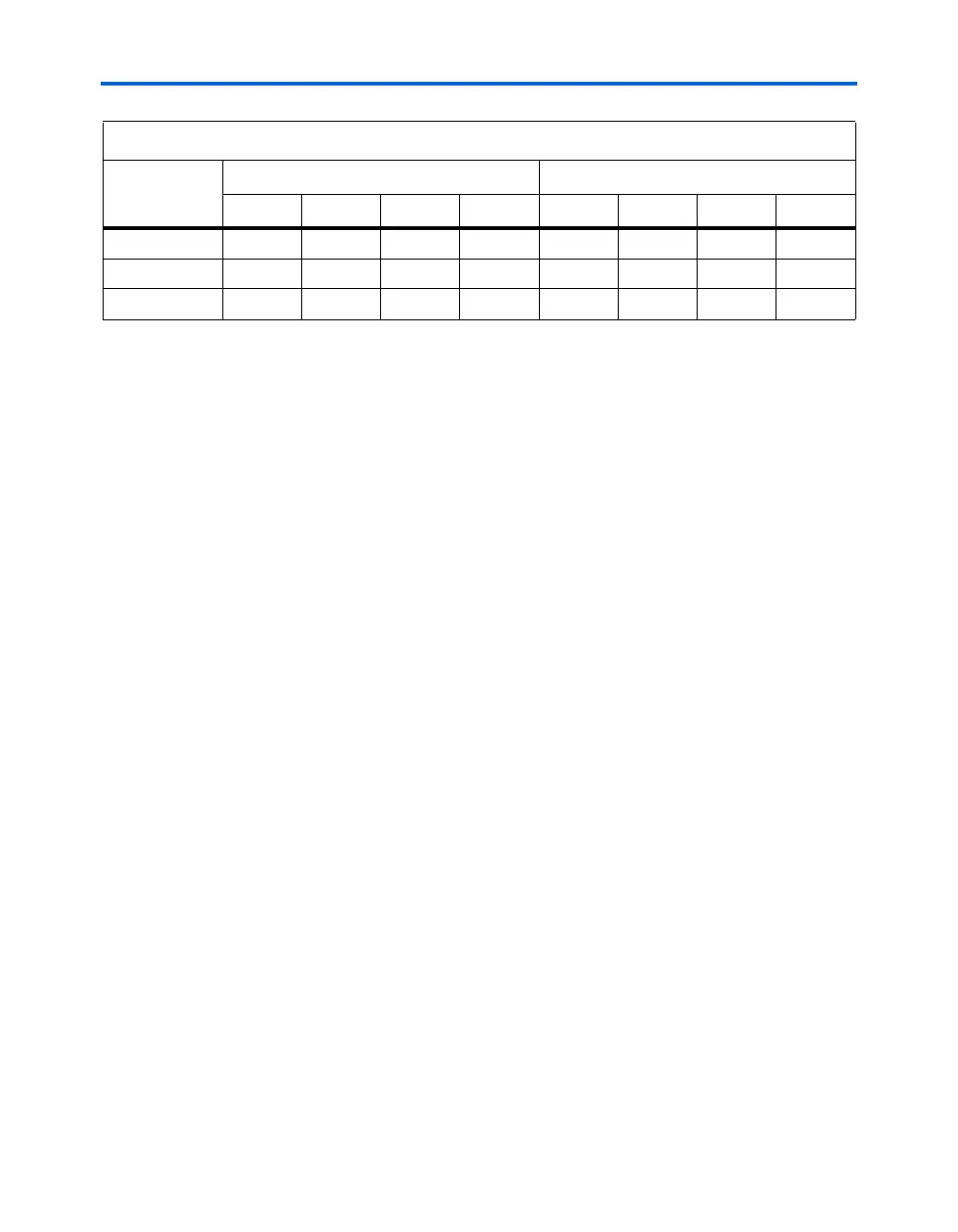

Table 5–4. Fast PLL Relationship with Stratix Clock Networks (Part 2 of 2) Notes (1), (2)

Output Signal

All Stratix Devices EP1S30 to EP1S80 Devices Only

PLL 1 PLL 2 PLL 3 PLL 4 PLL 7 PLL 8 PLL 9 PLL 10

Loading...

Loading...