Altera Corporation 2–7

July 2005 Stratix Device Handbook, Volume 2

TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices

Using TriMatrix

Memory

The TriMatrix memory blocks include input registers that synchronize

writes and output registers to pipeline designs and improve system

performance. All TriMatrix memory blocks are pipelined, meaning that

all inputs are registered, but outputs are either registered or

combinatorial. TriMatrix memory can emulate a flow-through memory

by using combinatorial outputs.

f For more information, see AN 210: Converting Memory from Asynchronous

to Synchronous for Stratix & Stratix GX Designs.

Depending on the TriMatrix memory block type, the memory can have

various modes, including:

■ Single-port

■ Simple dual-port

■ True dual-port (bidirectional dual-port)

■ Shift-register

■ ROM

■ FIFO

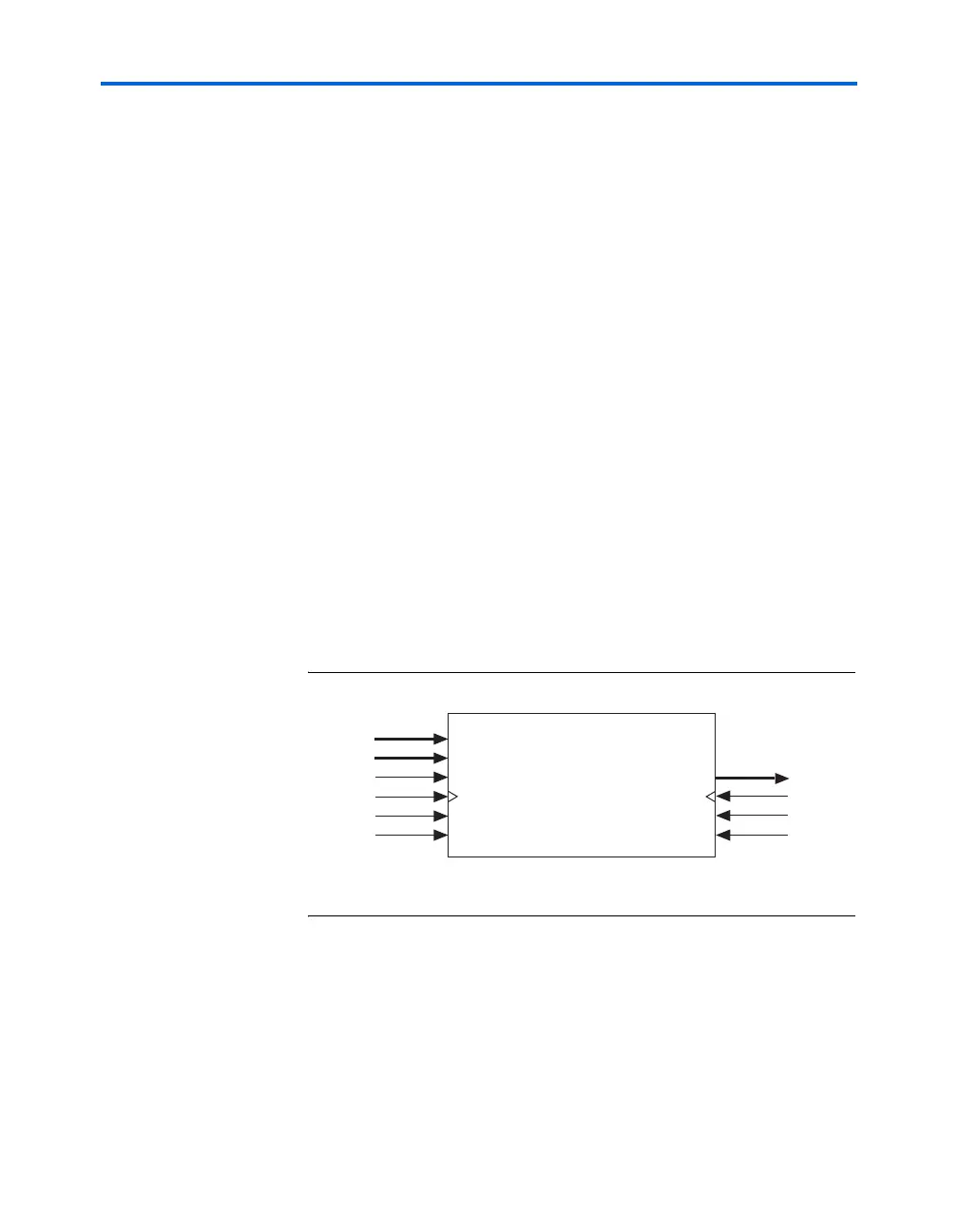

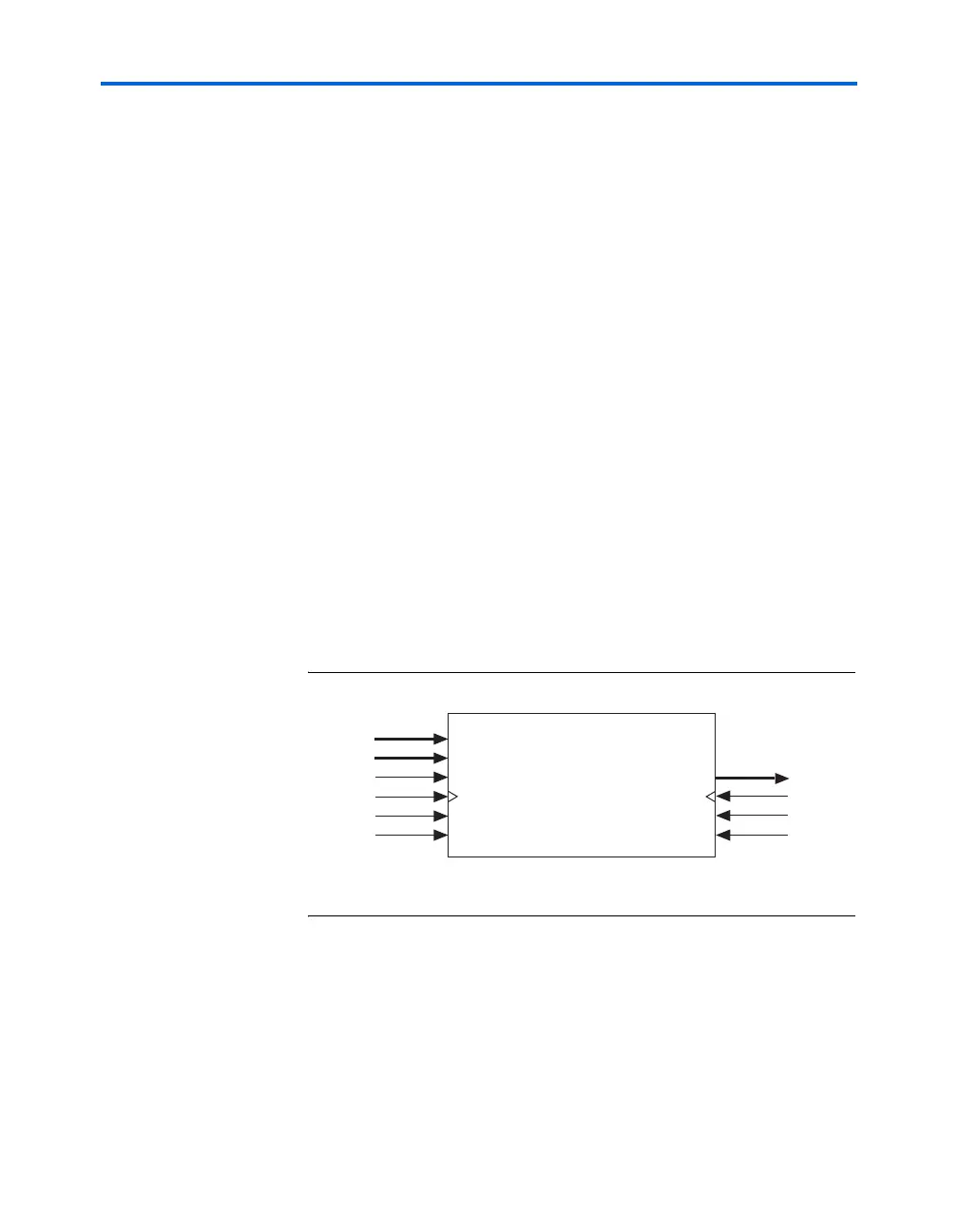

Implementing Single-Port Mode

Single-port mode supports non-simultaneous reads and writes.

Figure 2–2 shows the single-port memory configuration for TriMatrix

memory. All memory block types support the single-port mode.

Figure 2–2. Single-Port Memory Note (1)

Note to Figure 2–2:

(1) Two single-port memory blocks can be implemented in a single M4K block.

M4K memory blocks can also be divided in half and used for two

independent single-port RAM blocks. The Altera Quartus II software

automatically uses this single-port memory packing when running low

on memory resources. To force two single-port memories into one M4K

block, first ensure that each of the two independent RAM blocks is equal

to or less than half the size of the M4K block. Second, assign both single-

port RAMs to the same M4K block.

data[ ]

address[ ]

wren

inclock

inclocken

inaclr

q[ ]

outclock

outclocken

outaclr

Loading...

Loading...