11–30 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Configuration Schemes

PPA Configuration

In PPA schemes, a microprocessor drives data to the Stratix or Stratix GX

device through a download cable. When using a PPA scheme, use a 1-kΩ

pull-up resistor to pull the DCLK pin high to prevent unused

configuration pins from floating.

To begin configuration, the microprocessor drives nCONFIG high and

then asserts the target device’s nCS pin low and CS pin high. Next, the

microprocessor places an 8-bit configuration word on the target device’s

data inputs and pulses nWS low. On the rising edge of nWS, the target

device latches a byte of configuration data and then drives its RDYnBSY

signal low, indicating that it is processing the byte of configuration data.

The microprocessor then performs other system functions while the

Stratix or Stratix GX device is processing the byte of configuration data.

Next, the microprocessor checks nSTATUS and CONF_DONE. If nSTATUS

is high and CONF_DONE is low, the microprocessor sends the next data

byte. If nSTATUS is low, the device is signaling an error and the

microprocessor should restart configuration. However, if nSTATUS is

high and all the configuration data is received, the device is ready for

initialization. At the beginning of initialization, CONF_DONE goes high to

indicate that configuration is complete. The CONF_DONE pin must have

an external 10-kΩ pull-up resistor in order for the device to initialize.

Initialization, by default, uses an internal oscillator, which runs at

10 MHz. After initialization, this internal oscillator is turned off. When

initialization is complete, the Stratix or Stratix GX device enters user

mode.

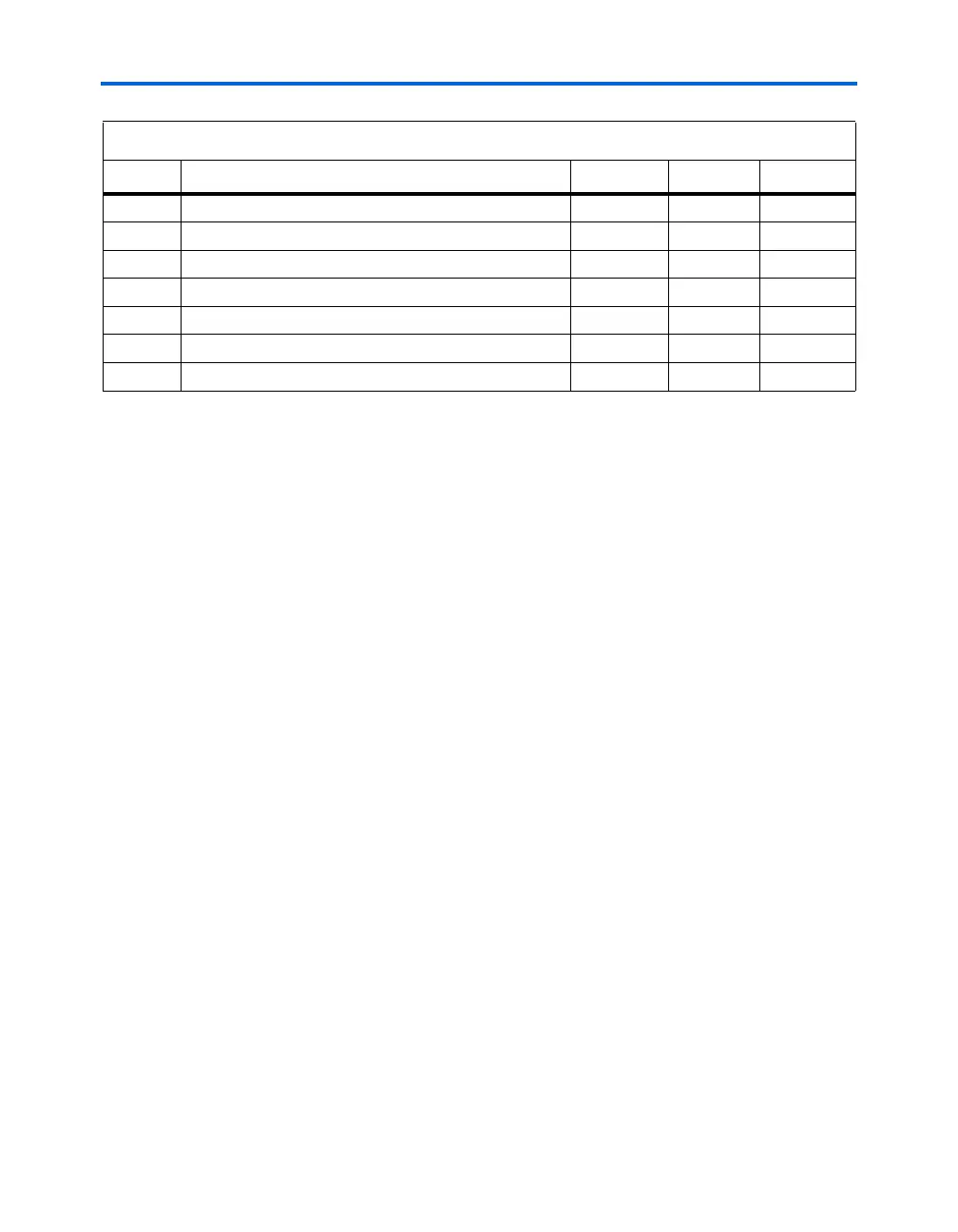

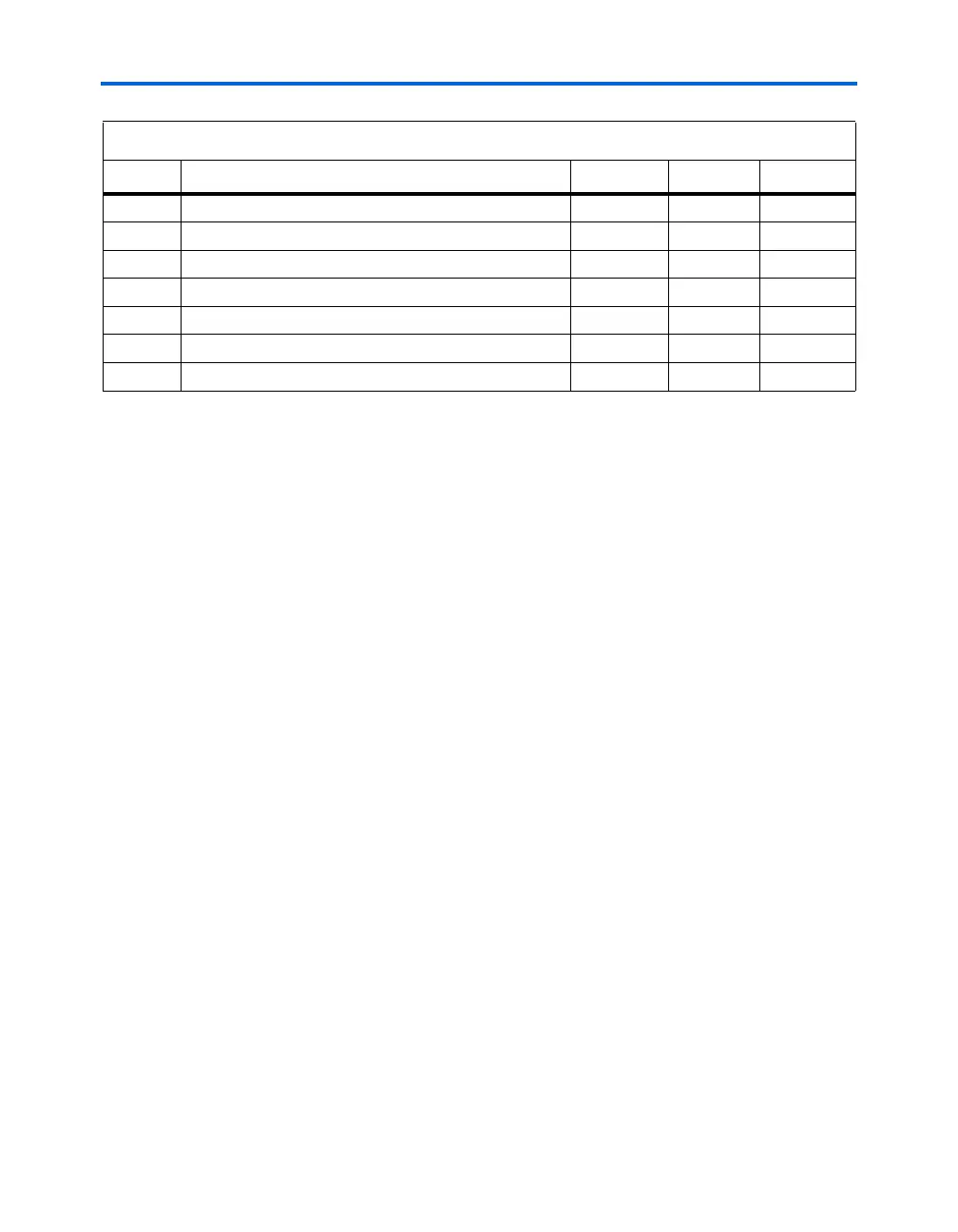

f

MAX

DCLK frequency

100 MHz

t

CD2UM

CONF_DONE high to user mode (1)

620µs

t

CF2CD

nCONFIG low to CONF_DONE low

800 ns

t

CF2ST0

nCONFIG low to nSTATUS low

800 ns

t

CF2ST1

nCONFIG high to nSTATUS high

40 (2) µs

t

STATUS

nSTATUS low pulse width

10 40 (2) µs

t

ST2CK

nSTATUS high to firstrising edge of DCLK

1µs

Notes to Ta b le 11 – 9:

(1) The minimum and maximum numbers apply only if the internal oscillator is chosen as the clock source for starting

up the device. If the clock source is CLKUSR, multiply the clock period by 136 to obtain this value.

(2) This value is obtainable if users do not delay configuration by extending the nSTATUS low pulse width.

Table 11–9. FPP Timing Parameters for Stratix & Stratix GX Devices (Part 2 of 2)

Symbol Parameter Min Max Units

Loading...

Loading...