4–14 Altera Corporation

Stratix Device Handbook, Volume 2 June 2006

Stratix & Stratix GX I/O Standards

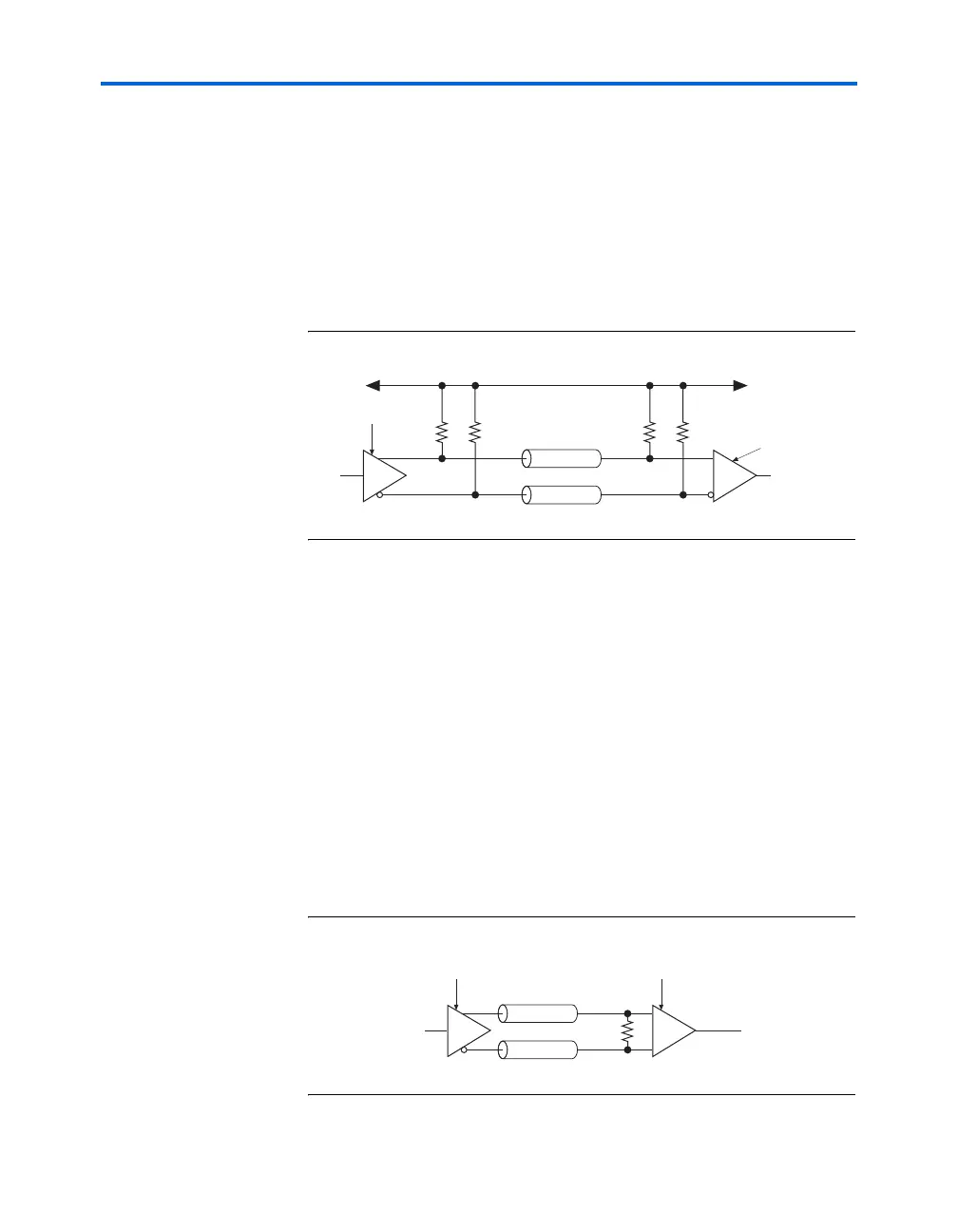

PCML standard is similar to LVPECL, but PCML has a reduced voltage

swing, which allows for a faster switching time and lower power

consumption. The PCML standard uses open drain outputs and requires

a differential output signal. See Figure 4–16 for details on PCML

termination. Stratix and Stratix GX devices support both input and

output levels.

Additionally, Stratix GX devices support 1.5-V PCML as described in the

Stratix GX Device Handbook, Volume 1.

Figure 4–16. PCML Termination

HyperTransport Technology - HyperTransport Consortium

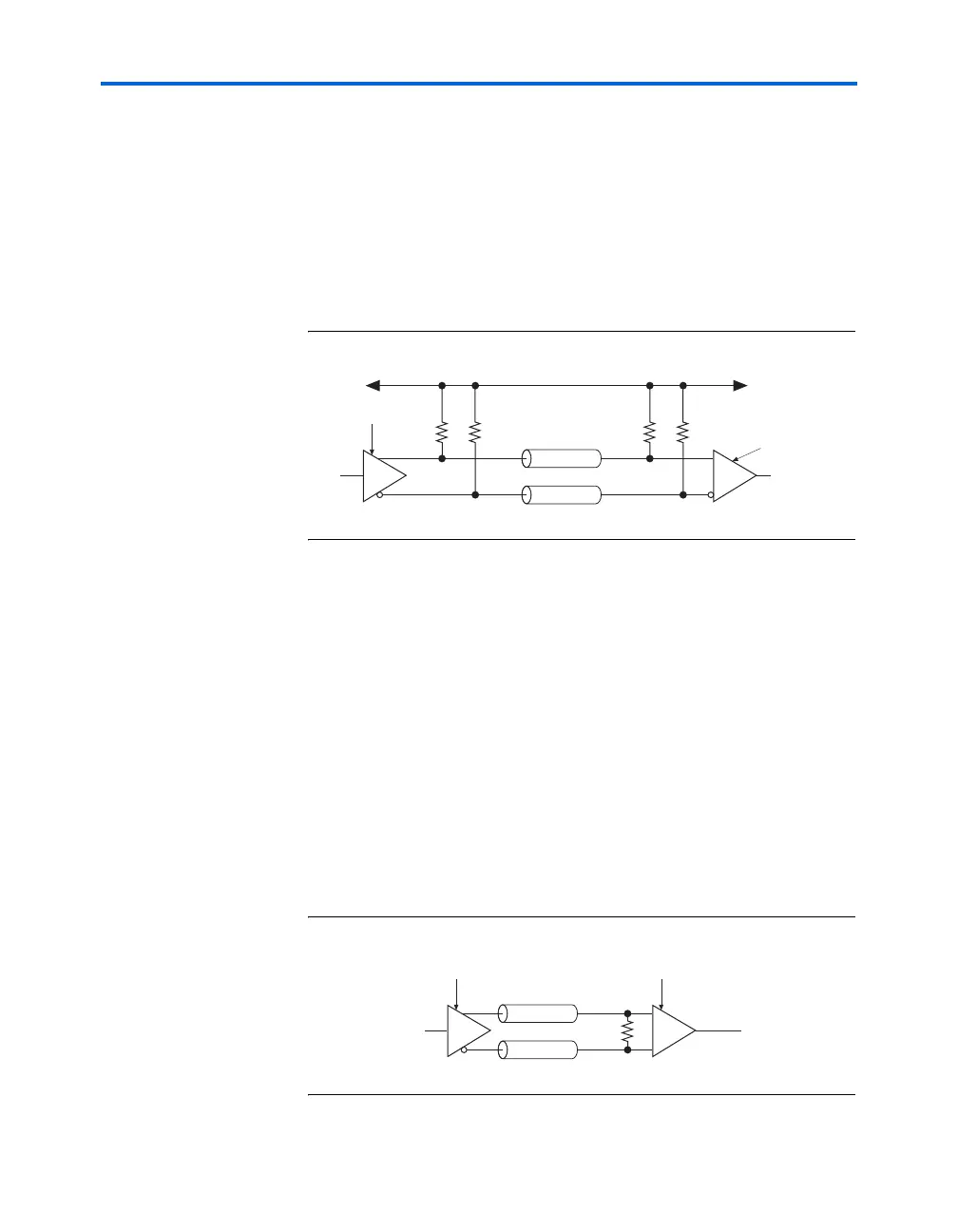

The HyperTransport technology I/O standard is a differential high-

speed, high-performance I/O interface standard requiring a 2.5-V V

CCIO

.

This standard is used in applications such as high-performance

networking, telecommunications, embedded systems, consumer

electronics, and Internet connectivity devices. The HyperTransport

technology I/O standard is a point-to-point standard in which each

HyperTransport technology bus consists of two point-to-point

unidirectional links. Each link is 2 to 32 bits. The HyperTransport

technology standard does not require an input reference voltage.

However, it does require a 100-Ω termination resistor between the two

signals at the input buffer. See Figure 4–17 for details on HyperTransport

technology termination. Stratix and Stratix GX devices support both

input and output levels.

Figure 4–17. HyperTransport Technology Termination

Output Buffer

Input Buffe

50 Ω 50 Ω

Z = 50 Ω

Z = 50 Ω

50 Ω 50 Ω

V

TT

Output Buffer Input Buffer

100 Ω

Z = 50 Ω

Z = 50 Ω

Loading...

Loading...