2–16 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Clock Modes

Implementing FIFO Buffers

While the small M512 memory blocks are ideal for designs with many

shallow FIFO buffers, all three memory sizes support FIFO mode.

All memory configurations have synchronous inputs; however, the FIFO

buffer outputs are always combinatorial. Simultaneous read and write

from an empty FIFO is not supported.

Clock Modes

Depending on the TriMatrix memory mode, independent, input/output,

read/write, and/or single-port clock modes are available. Table 2–12

shows the clock modes supported by the TriMatrix memory modes.

Independent Clock Mode

The TriMatrix memory blocks can implement independent clock mode

for true dual-port memory. In this mode, a separate clock is available for

each port (A and B). Clock A controls all registers on the port A side,

while clock B controls all registers on the port B side. Each port also

supports independent clock enables and asynchronous clear signals for

port A and B registers. Figure 2–9 shows a TriMatrix memory block in

independent clock mode.

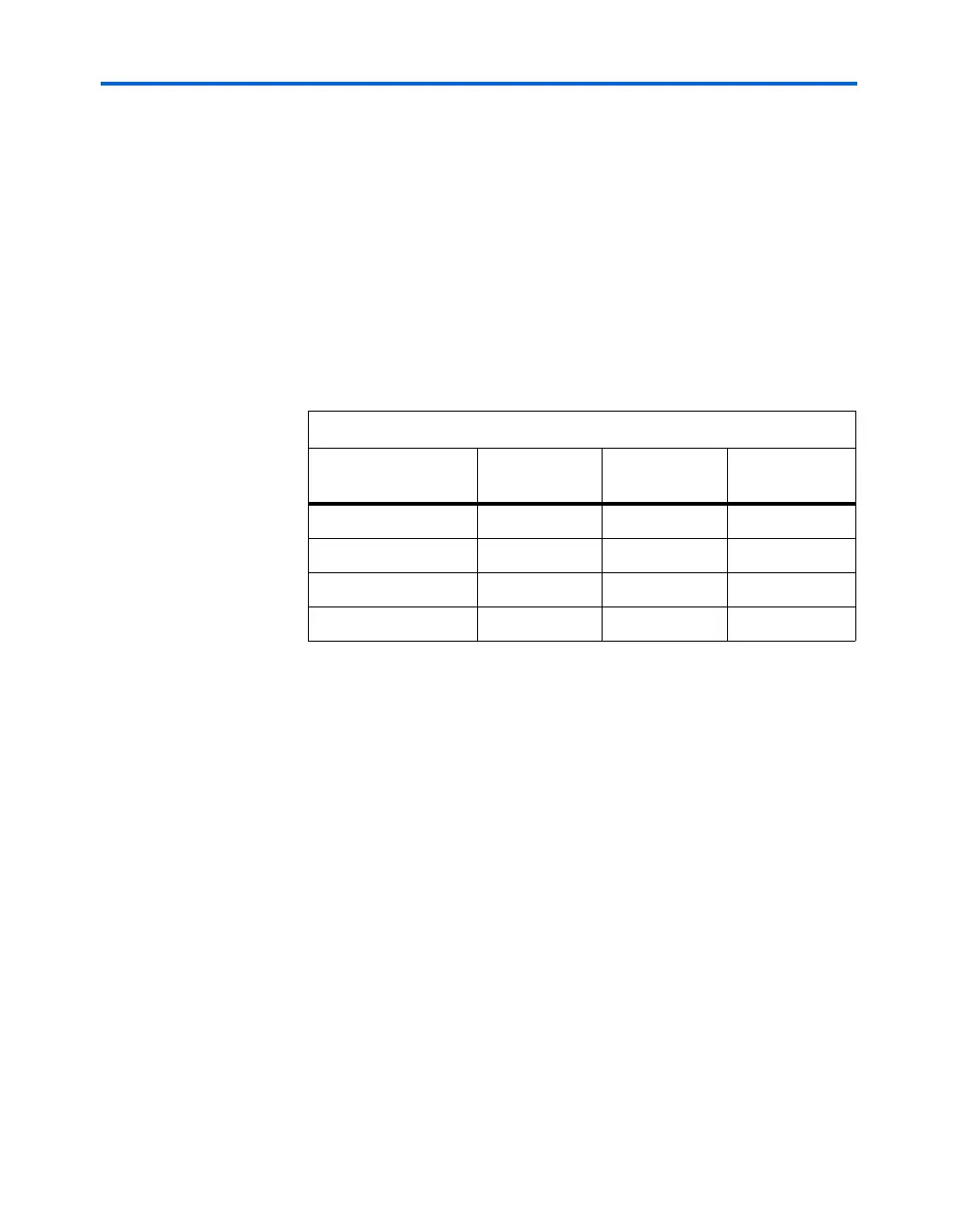

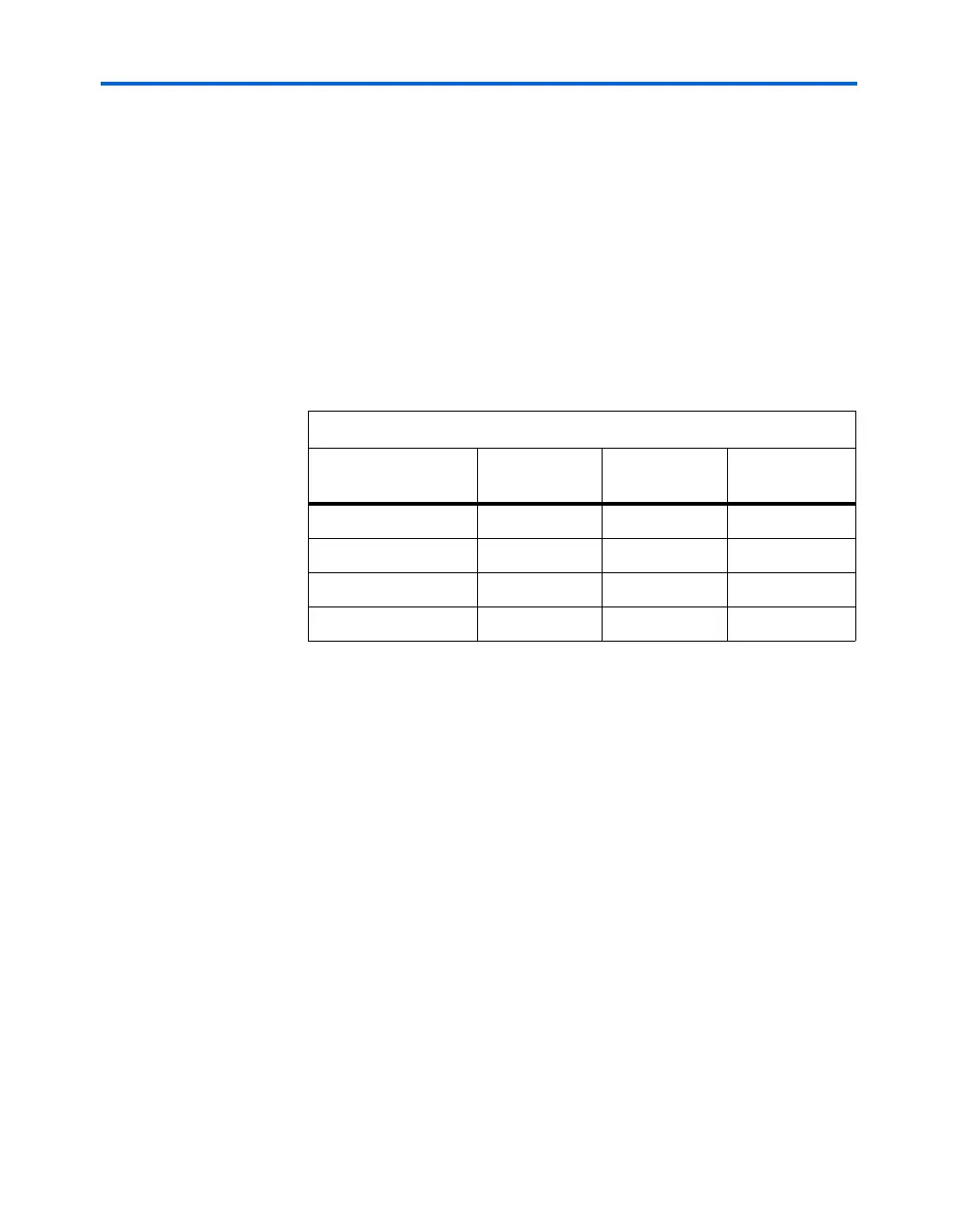

Table 2–12. TriMatrix Memory Clock Modes

Clocking Mode

True-Dual Port

Mode

Simple Dual-

Port Mode

Single-Port

Mode

Independent

v

Input/output

vv

Read/write

v

Single-port

v

Loading...

Loading...