Altera Corporation 2–17

July 2005 Stratix Device Handbook, Volume 2

TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices

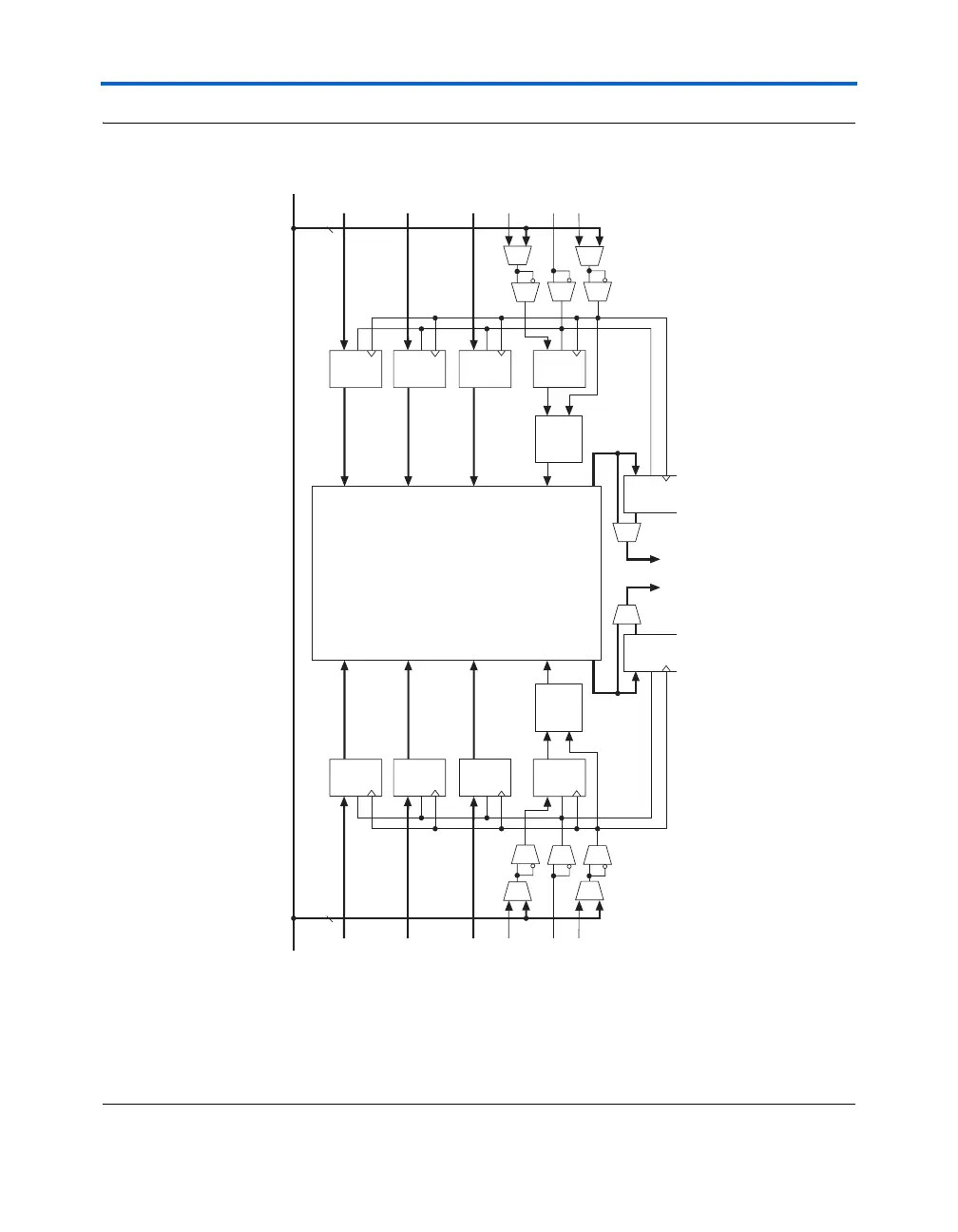

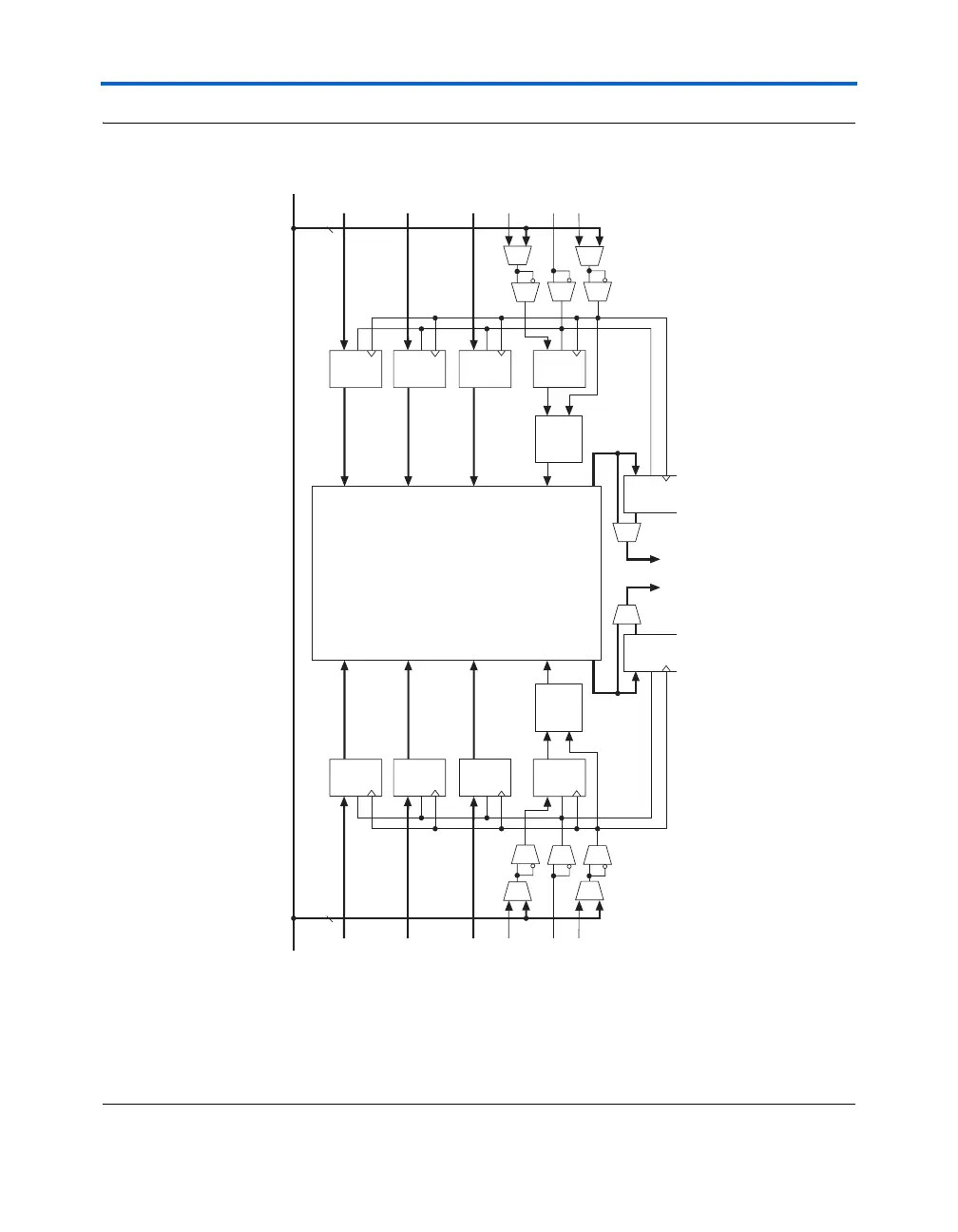

Figure 2–9. Independent Clock Mode Note (1), (2)

Note to Figure 2–9:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both

read and write operations.

(2) All registers shown have asynchronous clear ports, except when using the M-RAM. M-RAM blocks have

asynchronous clear ports on their output registers only.

8

D

ENA

Q

D

ENA

Q

D

ENA

Q

data

A

[ ]

address

A

[ ]

Memory Block

256 ´ 16 (2)

512 ´ 8

1,024 ´ 4

2,048 ´ 2

4,096 ´ 1

Data In

Address A

Write/Read

Enable

Data Out

Data In

Address B

Write/Read

Enable

Data Out

clken

A

clock

A

D

ENA

Q

wren

A

8 LAB Row Clocks

q

A

[ ]

8

data

B

[ ]

address

B

[ ]

clken

B

clock

B

wren

B

q

B

[ ]

ENA

AB

ENA

DQ

D

ENA

Q

byteena

A

[ ]

Byte Enable A

Byte Enable B

byteena

B

[ ]

ENA

DQ

ENA

DQ

ENA

DQ

DQ

Write

Pulse

Generator

Write

Pulse

Generator

Loading...

Loading...