Altera Corporation 2–11

July 2005 Stratix Device Handbook, Volume 2

TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices

M-RAM blocks have one write enable signal in simple dual-port mode. To

perform a write operation, the write enable is held high. The M-RAM

block is always enabled for read operation. If the read address and the

write address select the same address location during a write operation,

the M-RAM block output is unknown.

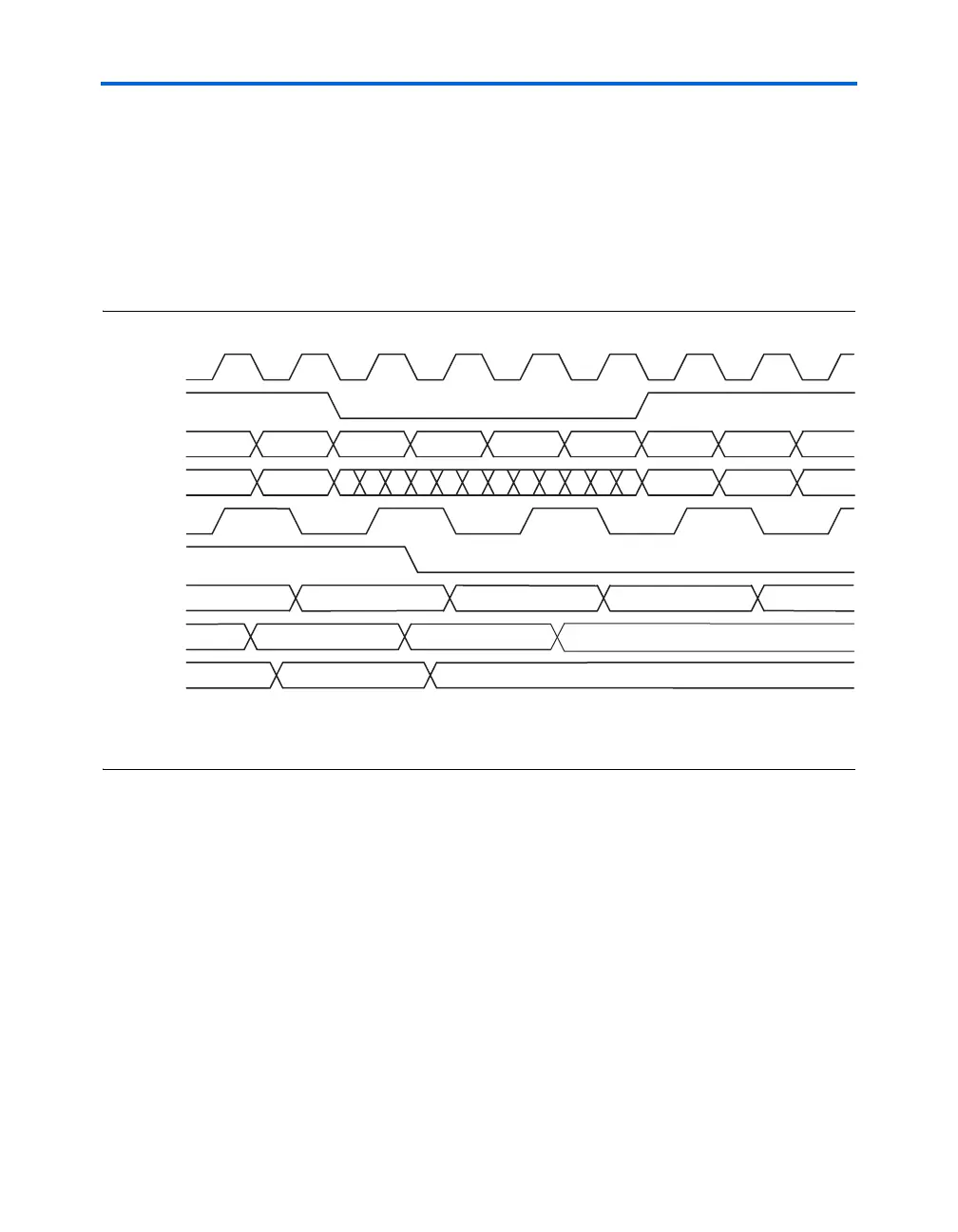

Figure 2–5 shows timing waveforms for read and write operations in

simple dual-port mode.

Figure 2–5. Simple Dual-Port Timing Waveforms Note (1)

Note to Figure 2–5:

(1) The rden signal is not available in the M-RAM block. A M-RAM block in simple dual-port mode is always reading

out the data stored at the current read address location.

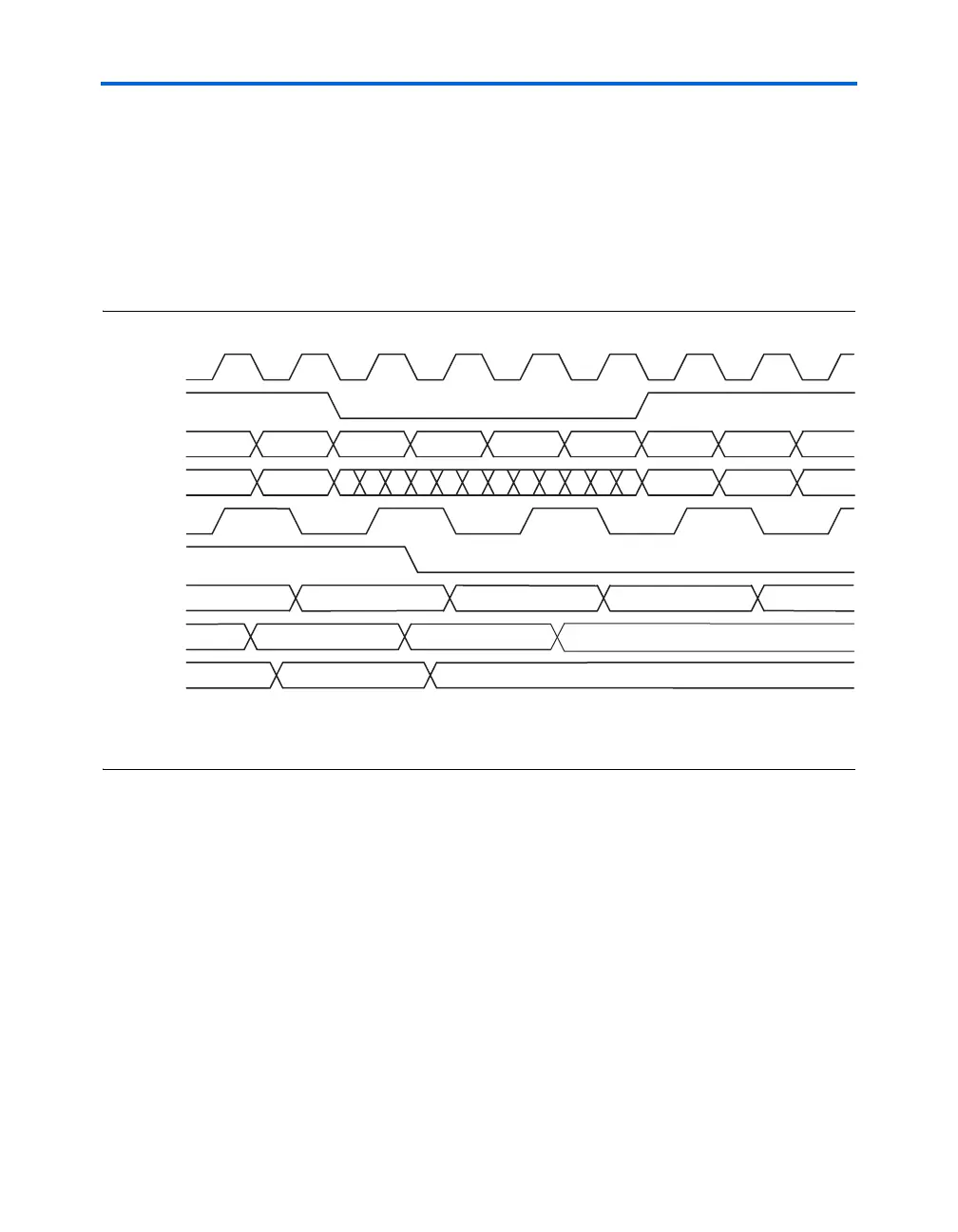

Implementing True Dual-Port Mode

M4K and M-RAM blocks offer a true dual-port mode to support any

combination of two-port operations: two reads, two writes, or one read

and one write at two different clock frequencies. Figure 2–6 shows the

true dual-port memory configuration for TriMatrix memory.

wrclock

wren

wraddress

data_in

synch_data_out

an-1

an a0 a1 a2 a3 a4 a5

din-1 din din4 din5

rdclock

a6

din6

asynch_data_out

rden

rdaddress

bn

b0

b1 b2 b3

doutn-2

doutn-1

doutn

doutn-1 doutn

dout0

dout0

Loading...

Loading...