Altera Corporation 2–15

July 2005 Stratix Device Handbook, Volume 2

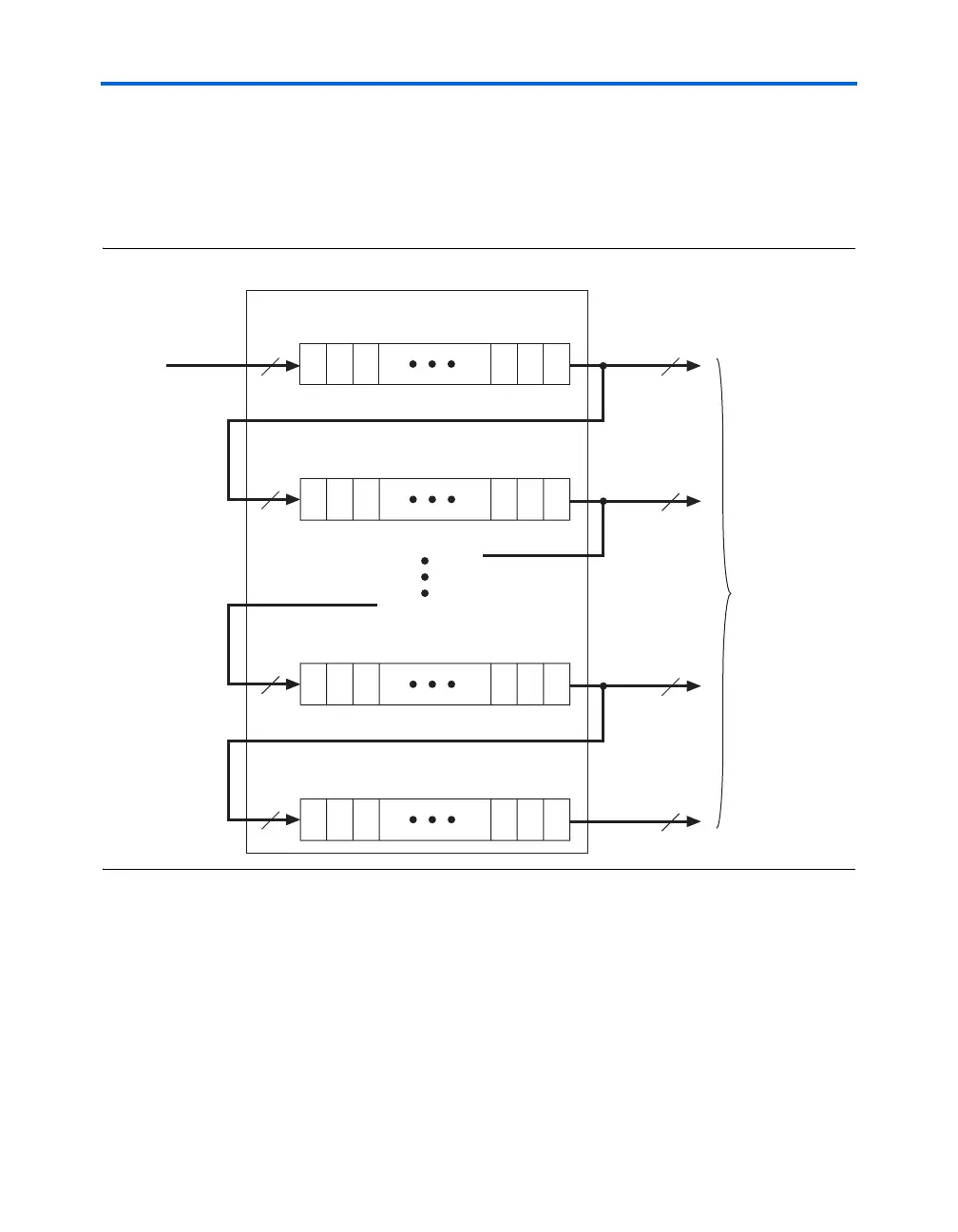

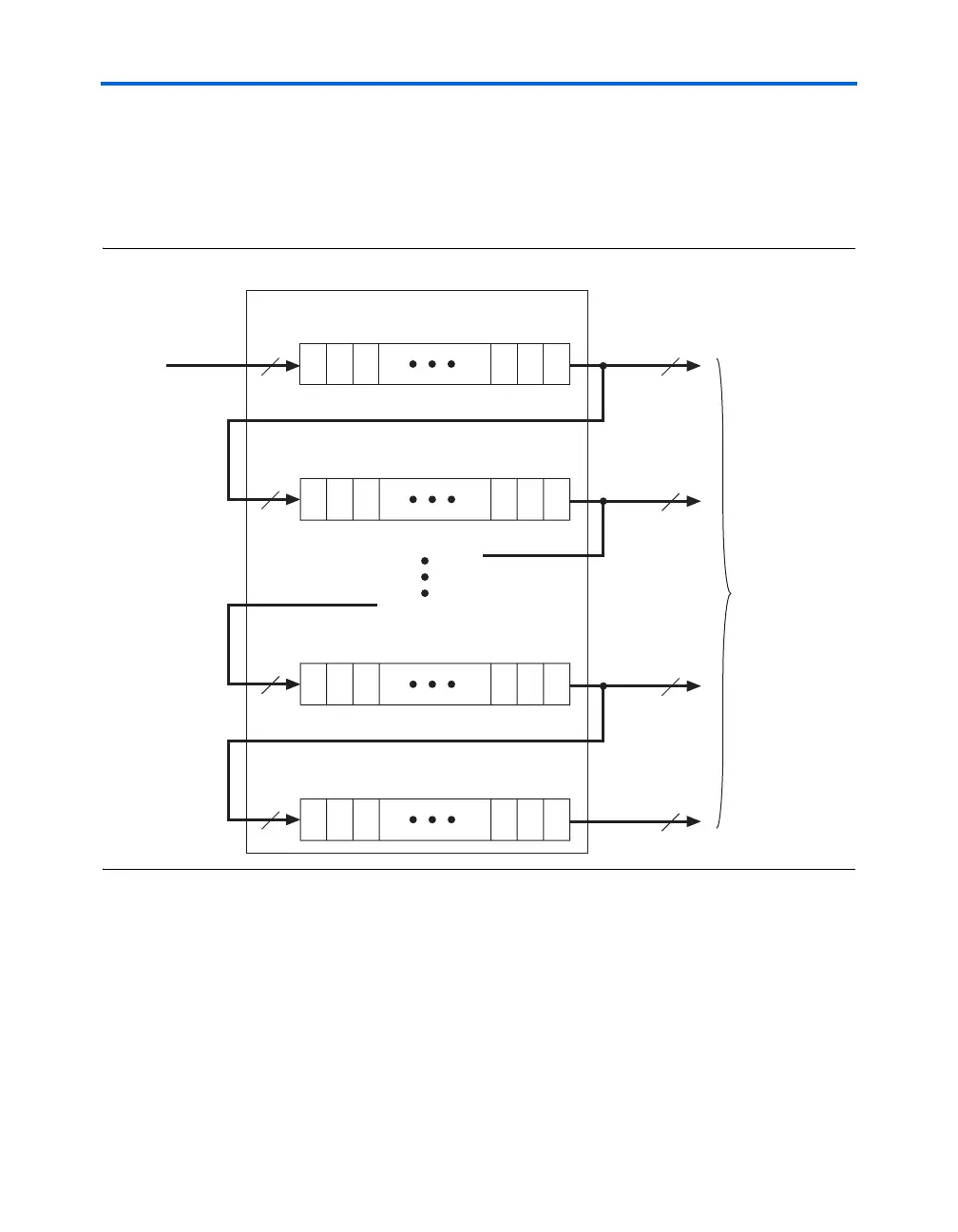

TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices

Data is written into each address location at the falling edge of the clock

and read from the address at the rising edge of the clock. The shift-register

mode logic automatically controls the positive and negative edge

clocking to shift the data in one clock cycle. Figure 2–8 shows the

TriMatrix memory block in the shift-register mode.

Figure 2–8. Shift-Register Memory Configuration

Implementing ROM Mode

The M512 and the M4K blocks support ROM mode. Use a memory

initialization file (.mif) to initialize the ROM contents of M512 and M4K

blocks. The M-RAM block does not support ROM mode.

All Stratix memory configurations must have synchronous inputs;

therefore, the address lines of the ROM are registered. The outputs can be

registered or combinatorial. The ROM read operation is identical to the

read operation in the single-port RAM configuration.

m-Bit Shift Register

w w

m-Bit Shift Register

m-Bit Shift Register

m-Bit Shift Register

w

w

w

w

w

w

w × m × n Shift Register

n Numbe

of Taps

Loading...

Loading...