Altera Corporation 13–3

July 2005 Stratix Device Handbook, Volume 2

Package Information for Stratix Devices

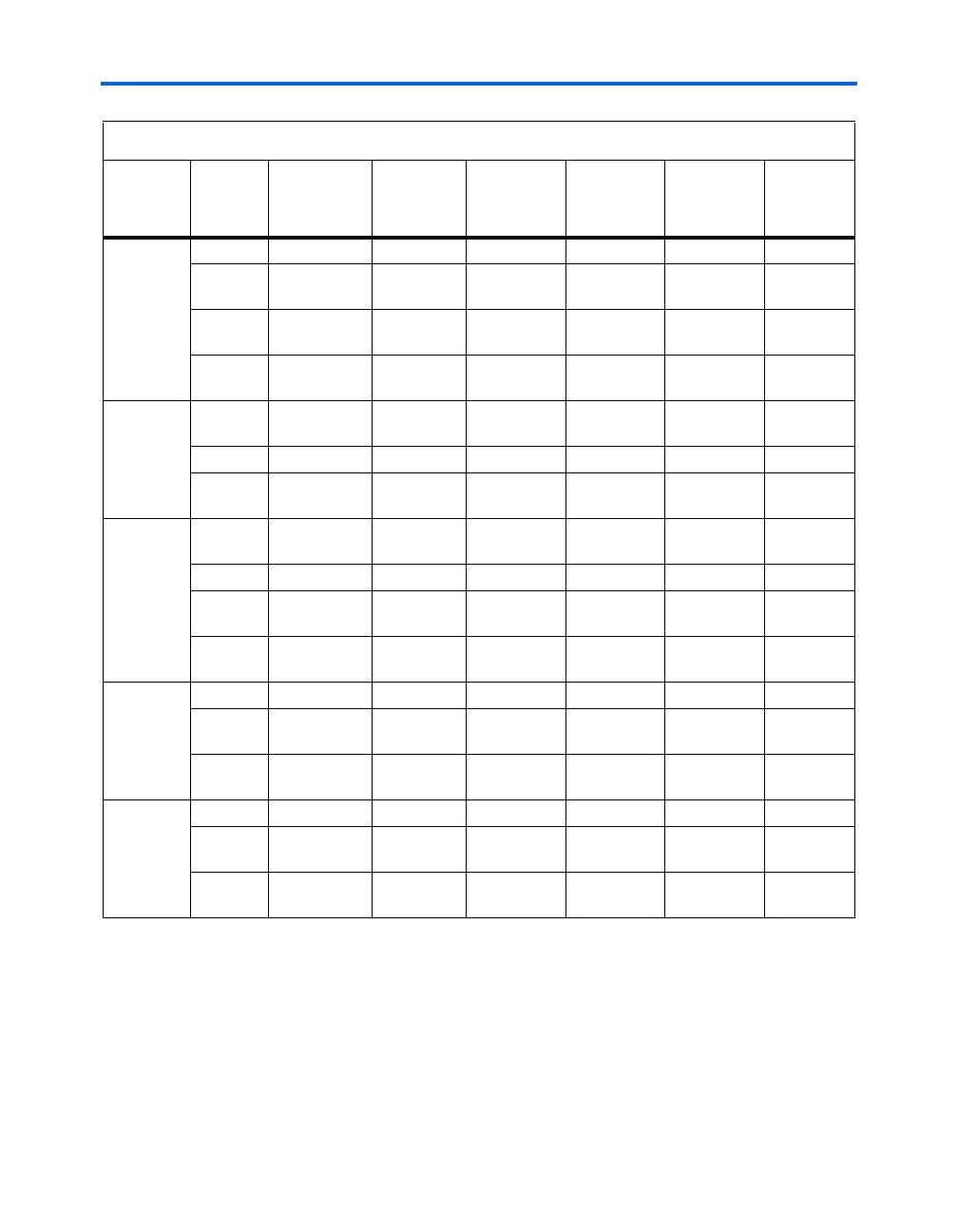

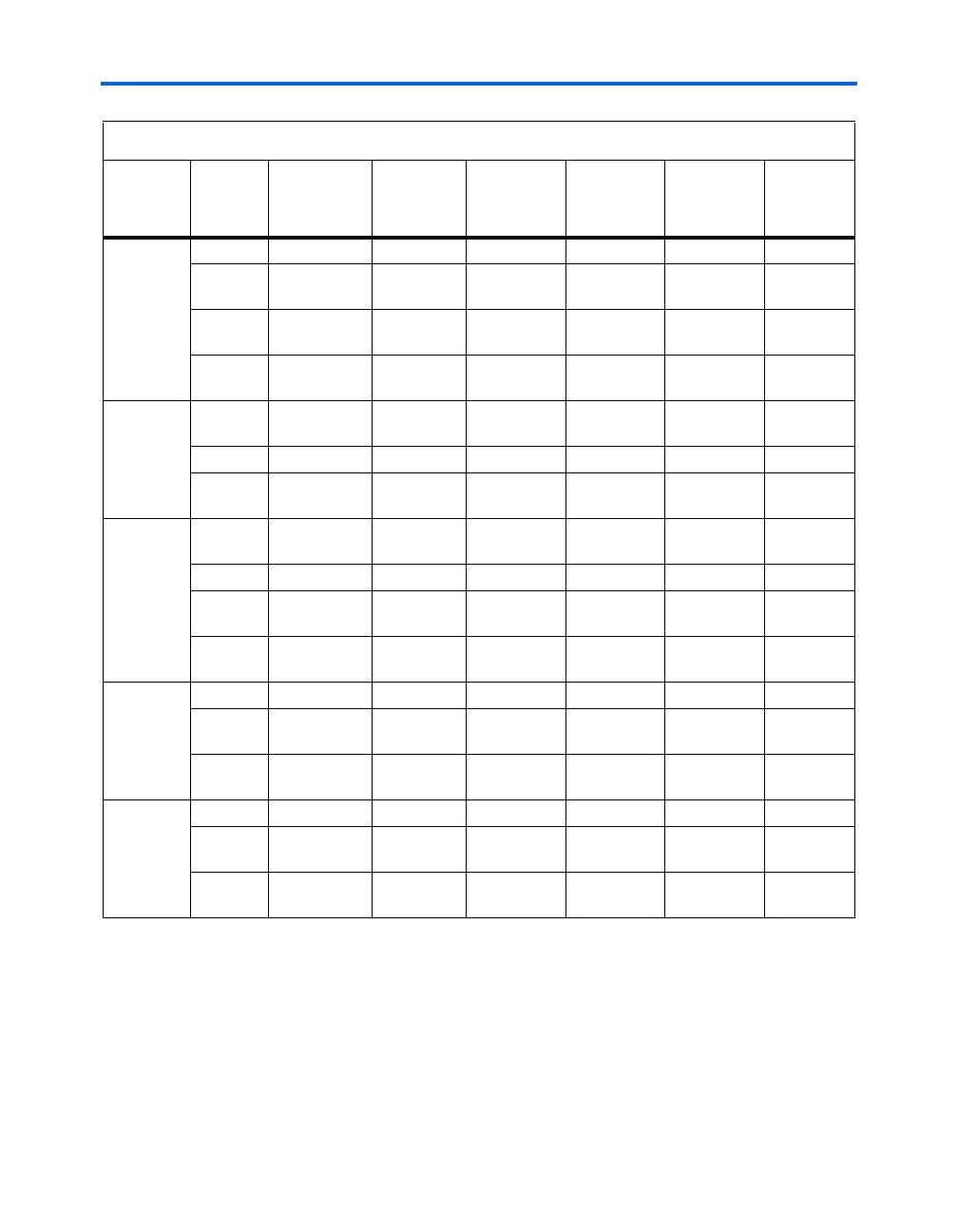

Package

Outlines

The package outlines on the following pages are listed in order of

ascending pin count. Altera package outlines meet the requirements of

JEDEC Publication No. 95.

EP1S25 672 BGA 2.2 14.8 11.7 10.0 8.7

672 FineLine

BGA

2.3 15.3 12 10.4 9

780 FineLine

BGA

0.25 10.5 8.5 7.1 6.0

1020 FineLine

BGA

0.25 10.0 8.0 6.6 5.5

EP1S30 780 FineLine

BGA

0.2 10.4 8.4 7.0 5.9

956 BGA 0.2 9.1 7.1 5.8 4.8

1020 FineLine

BGA

0.2 9.9 7.9 6.5 5.4

EP1S40 780 FineLine

BGA

0.17 10.4 8.3 6.9 5.8

956 BGA 0.18 9.0 7.0 5.7 4.7

1020 FineLine

BGA

0.17 9.8 7.8 6.4 5.3

1508 FineLine

BGA

0.18 9.1 7.1 5.8 4.7

EP1S60 956 BGA 0.13 8.9 6.9 5.6 4.6

1020 FineLine

BGA

0.13 9.7 7.7 6.3 5.2

1508 FineLine

BGA

0.13 8.9 7.0 5.6 4.6

EP1S80 956 BGA 0.1 8.8 6.8 5.5 4.5

1020 FineLine

BGA

0.1 9.6 7.6 6.2 5.1

1508 FineLine

BGA

0.1 8.8 6.9 5.5 4.5

Table 13–2. Thermal Resistance of Stratix Devices (Part 2 of 2)

Device Pin Count Package

θ

JC

(° C/W) θ

JA

(° C/W)

Still Air

θ

JA

(° C/W)

100 ft./min.

θ

JA

(° C/W)

200 ft./min.

θ

JA

(° C/W)

400

ft./min.

Loading...

Loading...