Altera Corporation 1–31

July 2005 Stratix Device Handbook, Volume 2

General-Purpose PLLs in Stratix & Stratix GX Devices

Fast PLLs

Stratix devices contain up to eight fast PLLs and Stratix GX devices

contain up to four fast PLLs. Both device PLLs have high-speed

differential I/O interface ability along with general-purpose features.

Figure 1–17 shows a diagram of the fast PLL. This section discusses the

PLL5_OUT[3..0]p/n

Single-ended or differential pins driven by extclk[3..0] ports from PLL 5.

PLL6_OUT[3..0]p/n

Single-ended or differential pins driven by extclk[3..0] ports from PLL 6.

PLL11_OUT, CLK13n

Single-ended output pin driven by clk0 port from PLL 11.

PLL12_OUT, CLK6n

Single-ended output pin driven by clk0 port from PLL 12.

VCCA_PLL5

Analog power for PLL 5. Connect this pin to 1.5 V, even if the PLL is not used.

VCCG_PLL5

Guard ring power for PLL 5. Connect this pin to 1.5 V, even if the PLL is not used.

GNDA_PLL5

Analog ground for PLL 5. You can connect this pin to the GND plane on the board.

GNDG_PLL5

Guard ring ground for PLL 5. You can connect this pin to the GND plane on the board.

VCCA_PLL6

Analog power for PLL 6. Connect this pin to 1.5 V, even if the PLL is not used.

VCCG_PLL6

Guard ring power for PLL 6. Connect this pin to 1.5 V, even if the PLL is not used.

GNDA_PLL6

Analog ground for PLL 6. You can connect this pin to the GND plane on the board.

GNDG_PLL6

Guard ring ground for PLL 6. You can connect this pin to the GND plane on the board.

VCCA_PLL11

Analog power for PLL 11. Connect this pin to 1.5 V, even if the PLL is not used.

VCCG_PLL11

Guard ring power for PLL 11. Connect this pin to 1.5 V, even if the PLL is not used.

GNDA_PLL11

Analog ground for PLL 11. You can connect this pin to the GND plane on the board.

GNDG_PLL11

Guard ring ground for PLL 11.You can connect this pin to the GND plane on the board.

VCCA_PLL12

Analog power for PLL 12. Connect this pin to 1.5 V, even if the PLL is not used.

VCCG_PLL12

Guard ring power for PLL 12. Connect this pin to 1.5 V, even if the PLL is not used.

GNDA_PLL12

Analog ground for PLL 12. You can connect this pin to the GND plane on the board.

GNDG_PLL12

Guard ring ground for PLL 12. You can connect this pin to the GND plane on the board.

VCC_PLL5_OUTA

External clock output V

CCIO

power for PLL5_OUT0p, PLL5_OUT0n, PLL5_OUT1p,

and PLL5_OUT1n outputs from PLL 5.

VCC_PLL5_OUTB

External clock output V

CCIO

power for PLL5_OUT2p, PLL5_OUT2n, PLL5_OUT3p,

and PLL5_OUT3n outputs from PLL 5.

VCC_PLL6_OUTA

External clock output V

CCIO

power for PLL5_OUT0p, PLL5_OUT0n, PLL5_OUT1p,

and PLL5_OUT1n outputs from PLL 6.

VCC_PLL6_OUTB

External clock output V

CCIO

power for PLL5_OUT2p, PLL5_OUT2n, PLL5_OUT3p,

and PLL5_OUT3n outputs from PLL 6.

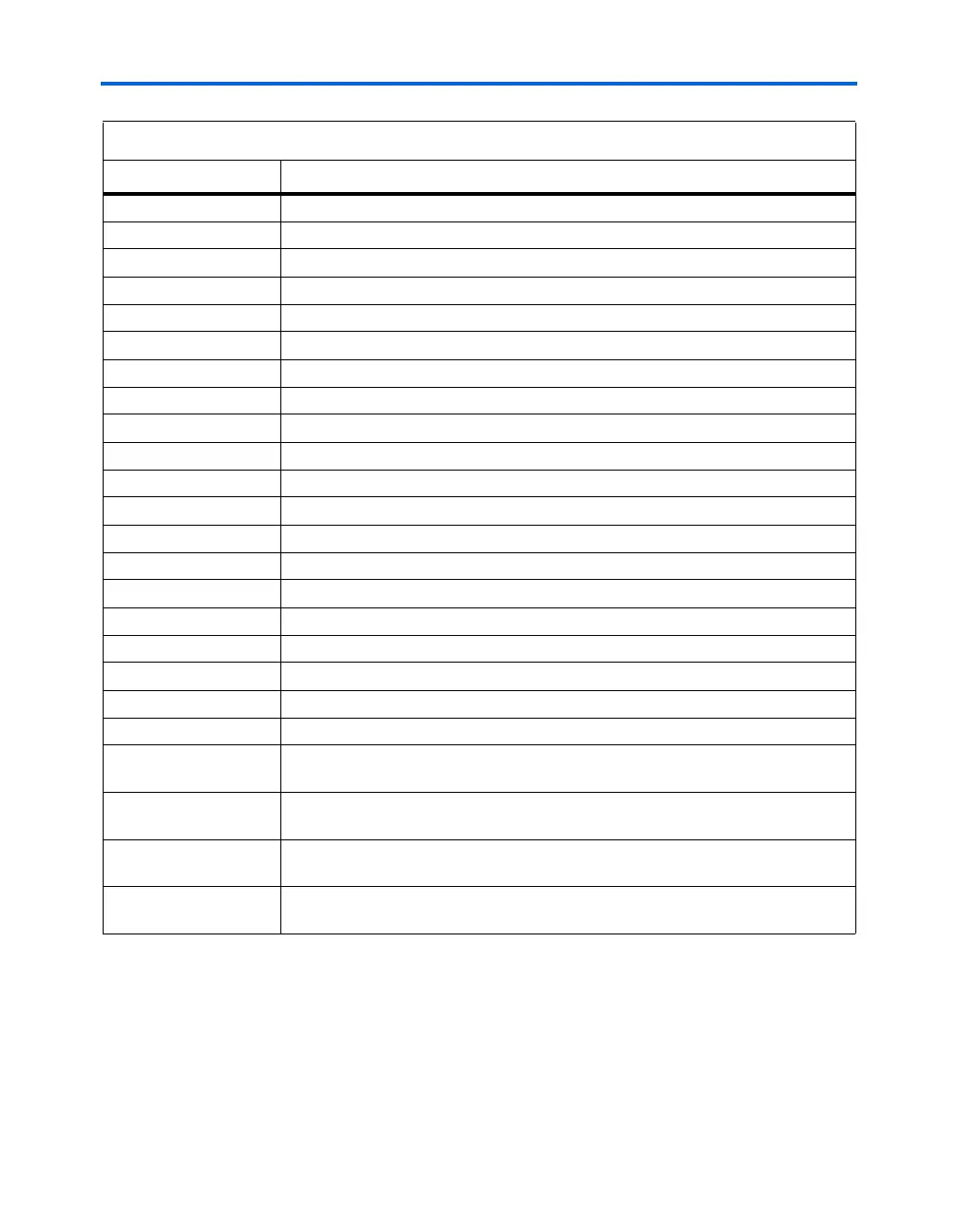

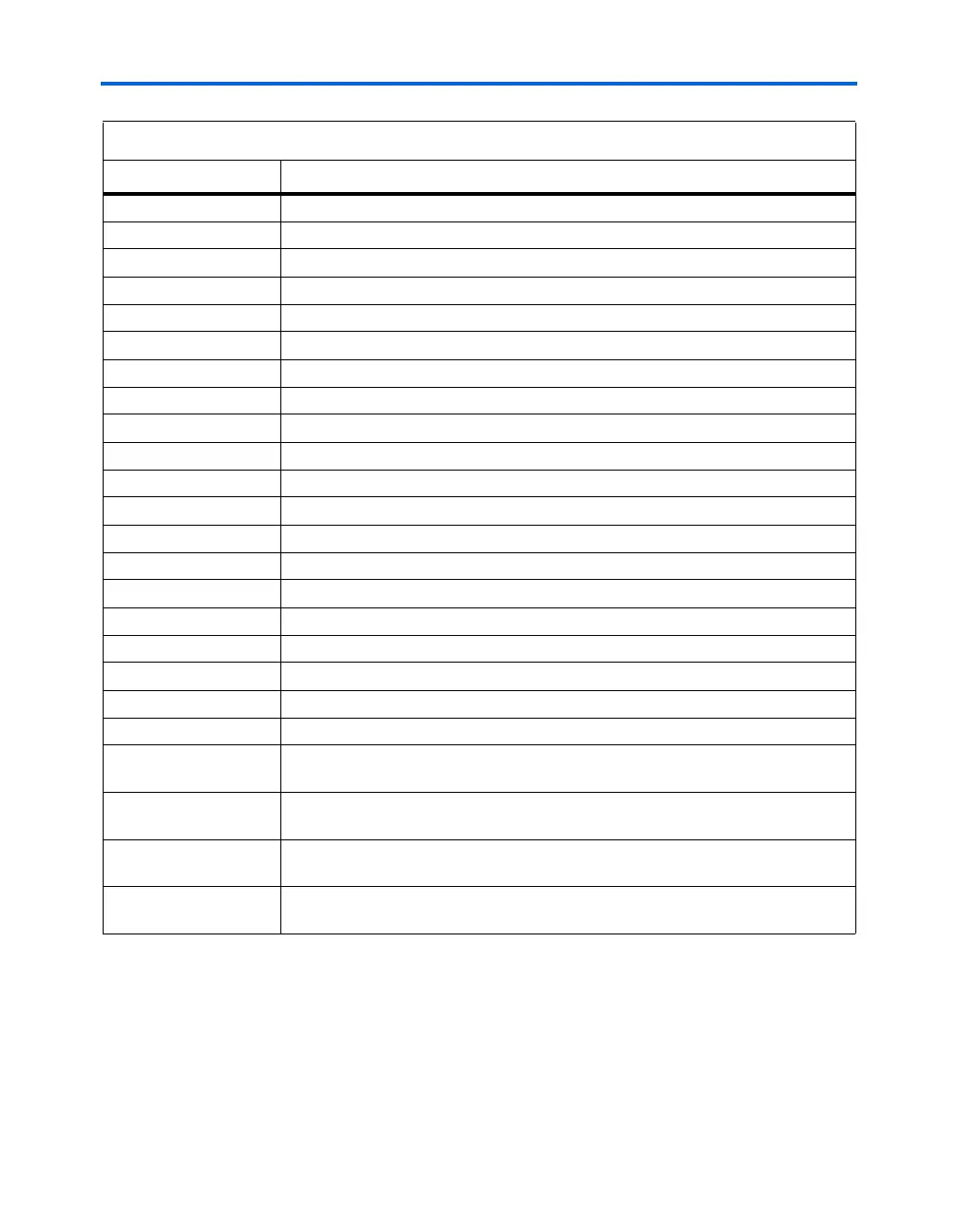

Table 1–9. Enhanced PLL Pins (Part 2 of 2)

Pin Description

Loading...

Loading...