5–32 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

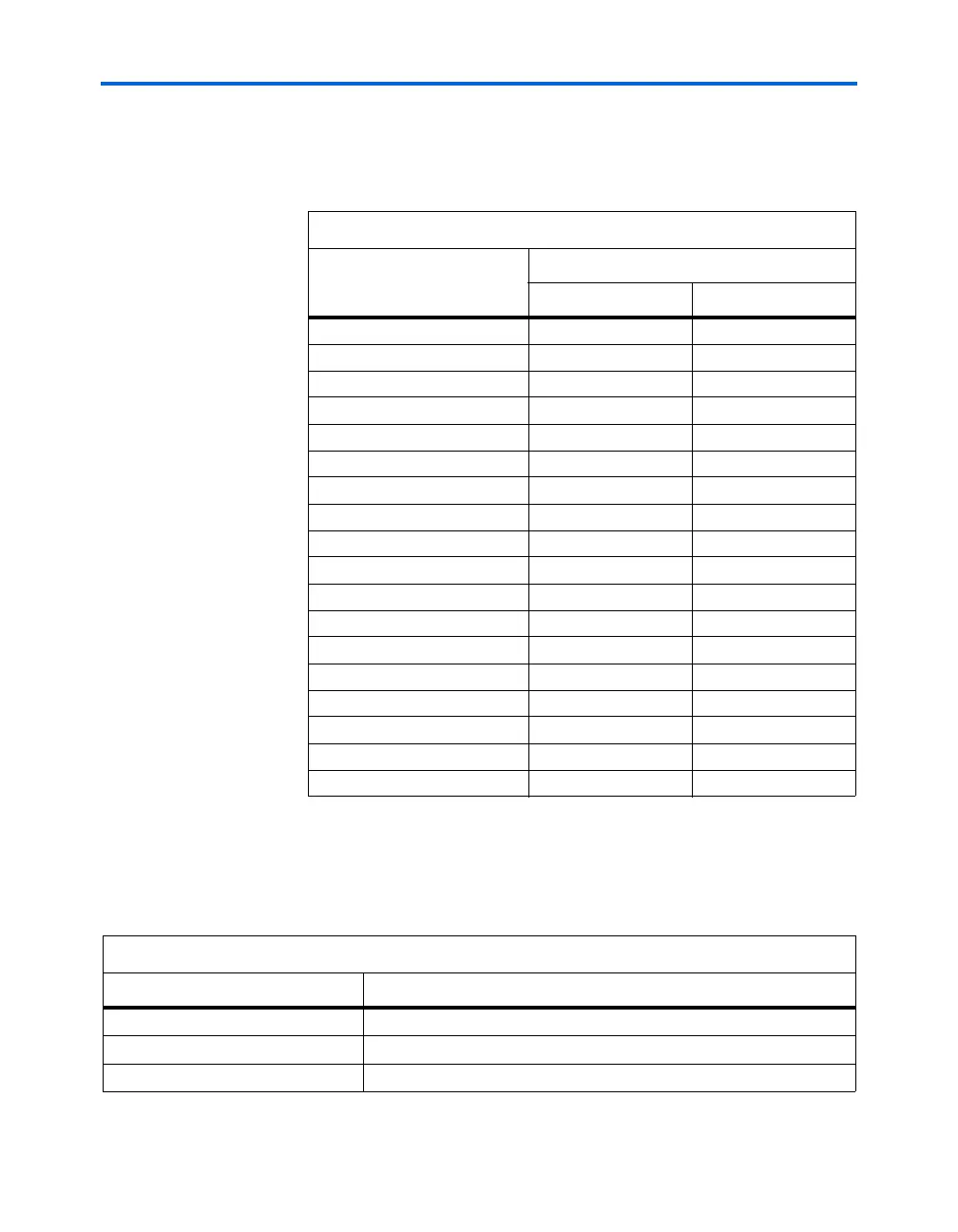

Source-Synchronous Timing Budget

Table 5–5 shows the conventions for differential bit naming for

18 differential channels. However, the MSB and LSB are increased with

the number of channels used in a system.

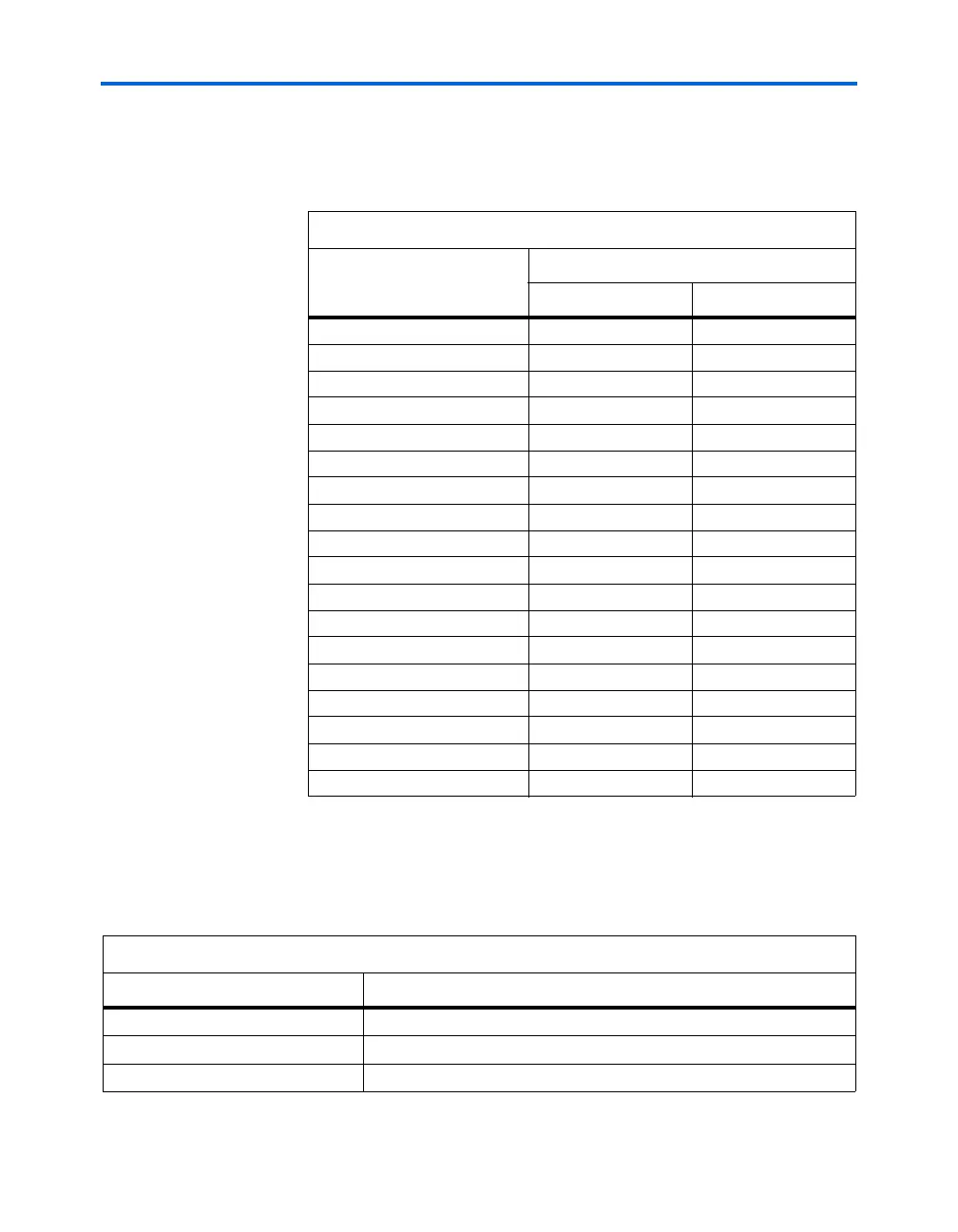

Timing Definition

The specifications used to define high-speed timing are described in

Table 5–6.

Table 5–5. LVDS Bit Naming

Receiver Data Channel

Number

Internal 8-Bit Parallel Data

MSB Position LSB Position

170

2158

32316

43124

53932

64740

75548

86356

97164

10 79 72

11 87 80

12 95 88

13 103 96

14 111 104

15 119 112

16 127 120

17 135 128

18 143 136

Table 5–6. High-Speed Timing Specifications & Terminology (Part 1 of 2)

High-Speed Timing Specification Terminology

t

C

High-speed receiver/transmitter input and output clock period.

f

HSCLK

High-speed receiver/transmitter input and output clock frequency.

t

RISE

Low-to-high transmission time.

Loading...

Loading...