Altera Corporation 5–33

July 2005 Stratix Device Handbook, Volume 2

High-Speed Differential I/O Interfaces in Stratix Devices

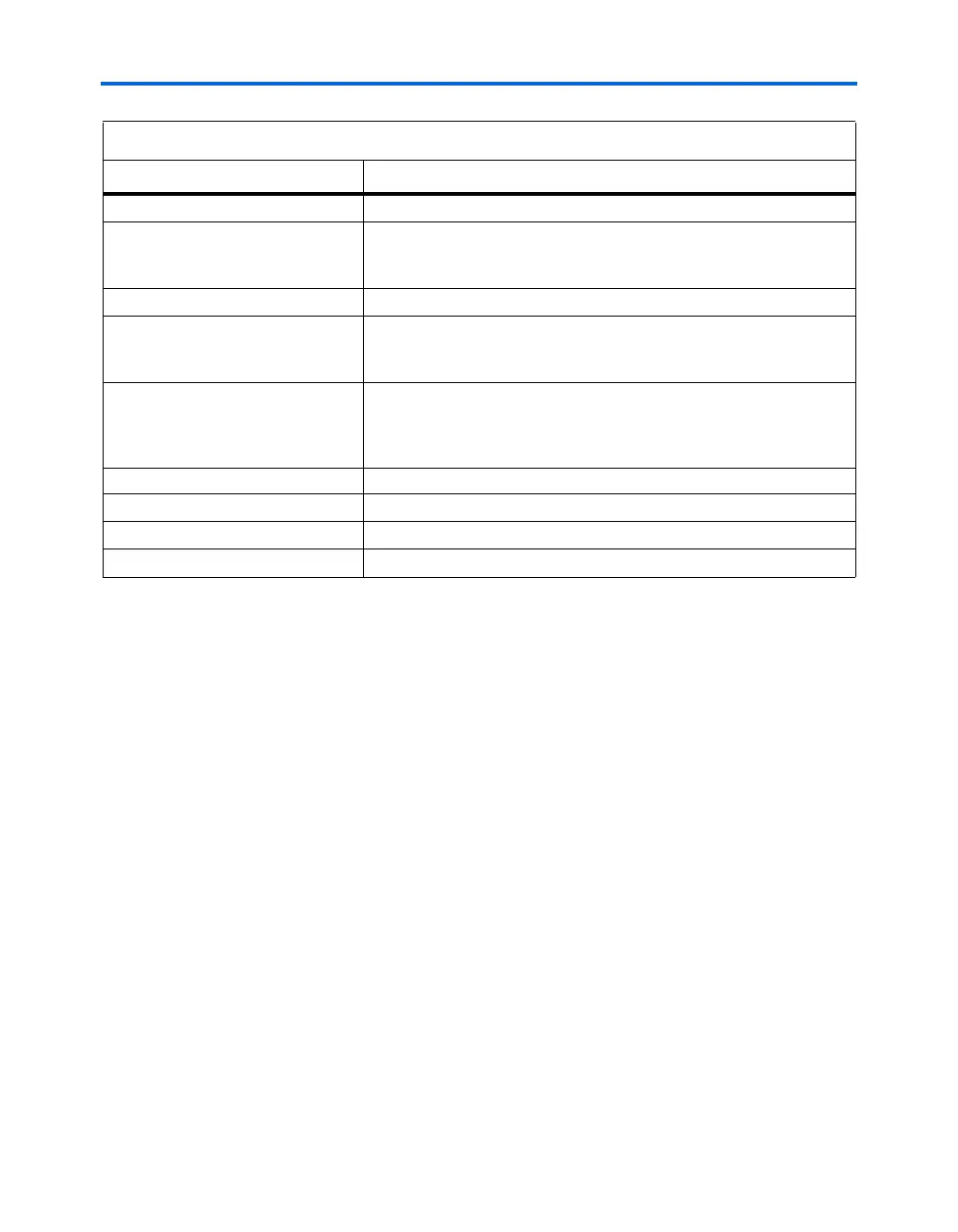

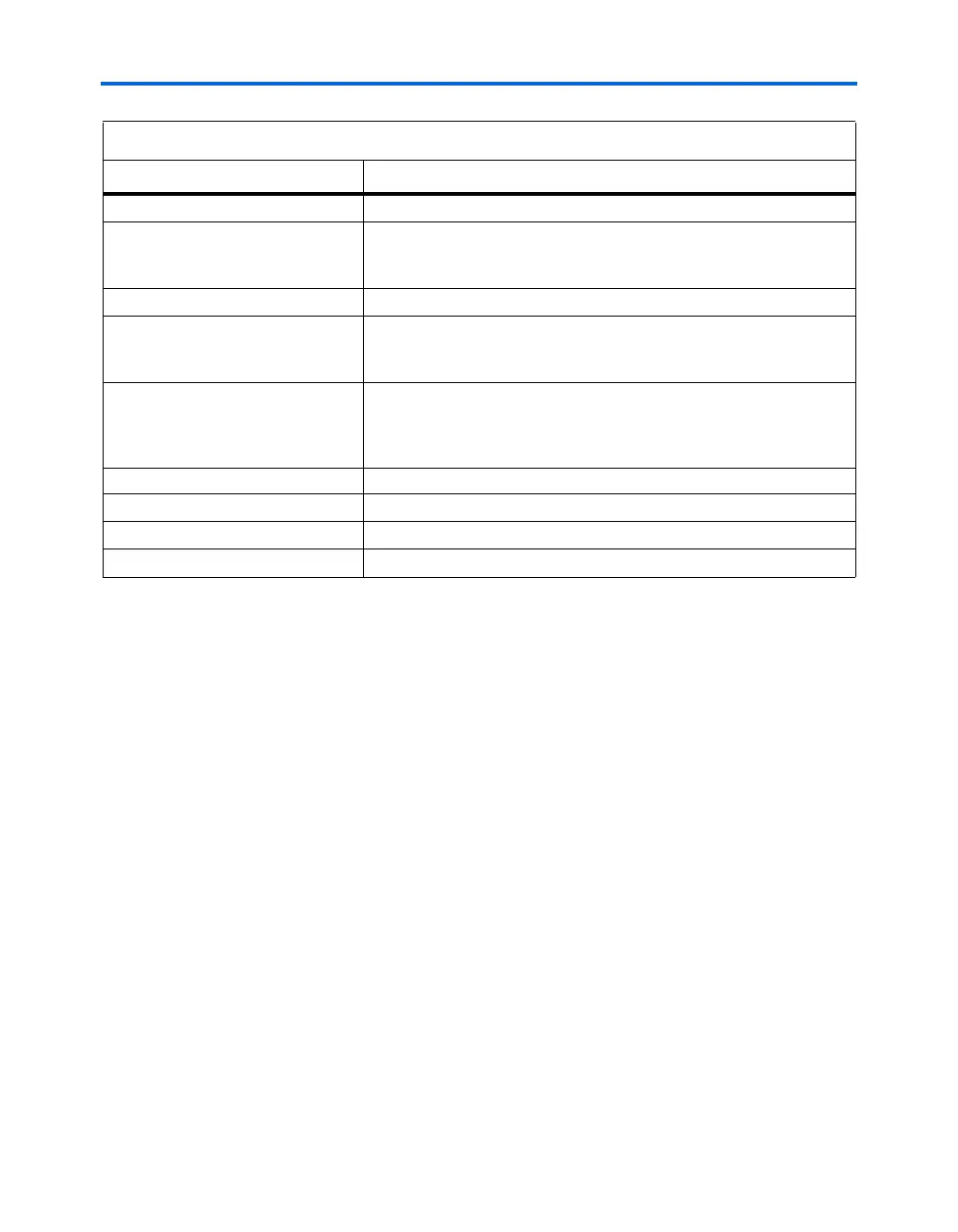

t

FALL

High-to-low transmission time.

Timing unit interval (TUI) The timing budget allowed for skew, propagation delays, and data

sampling window. (TUI = 1/(Receiver Input Clock Frequency ×

Multiplication Factor) = t

C

/w).

f

HSDR

Maximum LVDS data transfer rate (f

HSDR

= 1/TUI).

Channel-to-channel skew (TCCS) The timing difference between the fastest and slowest output edges,

including t

CO

variation and clock skew. The clock is included in the TCCS

measurement.

Sampling window (SW) The period of time during which the data must be valid in order for you to

capture it correctly. The setup and hold times determine the ideal strobe

position within the sampling window.

SW = t

SW

(max) – t

SW

(min).

Input jitter (peak-to-peak) Peak-to-peak input jitter on high-speed PLLs.

Output jitter (peak-to-peak) Peak-to-peak output jitter on high-speed PLLs.

t

DUTY

Duty cycle on high-speed transmitter output clock.

t

LOCK

Lock time for high-speed transmitter and receiver PLLs.

Table 5–6. High-Speed Timing Specifications & Terminology (Part 2 of 2)

High-Speed Timing Specification Terminology

Loading...

Loading...