2–12 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Using TriMatrix Memory

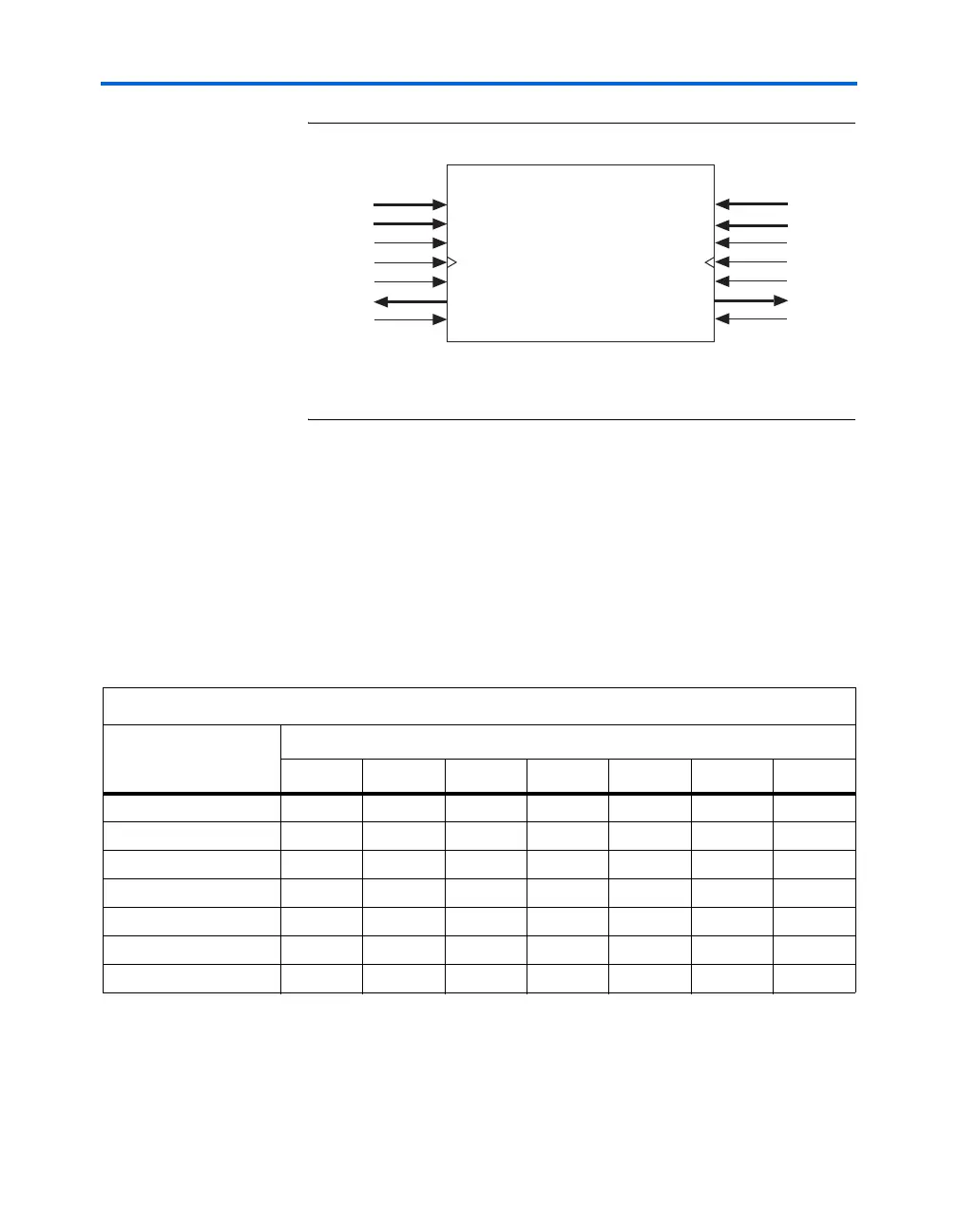

Figure 2–6. True Dual-Port Memory Note (1)

Note to Figure 2–6:

(1) True dual-port memory supports input/output clock mode in addition to the

independent clock mode shown.

The widest bit configuration of the M4K and M-RAM blocks in true dual-

port mode is 256 × 16-bit (× 18-bit with parity) and 8K × 64-bit (× 72-bit

with parity), respectively. The 128 × 32-bit (× 36-bit with parity)

configuration of the M4K block and the 4K × 128-bit (× 144-bit with parity)

configuration of the M-RAM block are unavailable because the number of

output drivers is equivalent to the maximum bit width of the respective

memory block. Because true dual-port RAM has outputs on two ports,

the maximum width of the true dual-port RAM equals half of the total

number of output drivers. Tables 2–10 and 2–11 list the possible M4K

RAM block and M-RAM block configurations, respectively.

data

A

[ ]

address

A

[ ]

wren

A

clock

A

clocken

A

q

A

[ ]

aclr

A

data

B

[ ]

address

B

[ ]

wren

B

clock

B

clocken

B

q

B

[ ]

aclr

B

AB

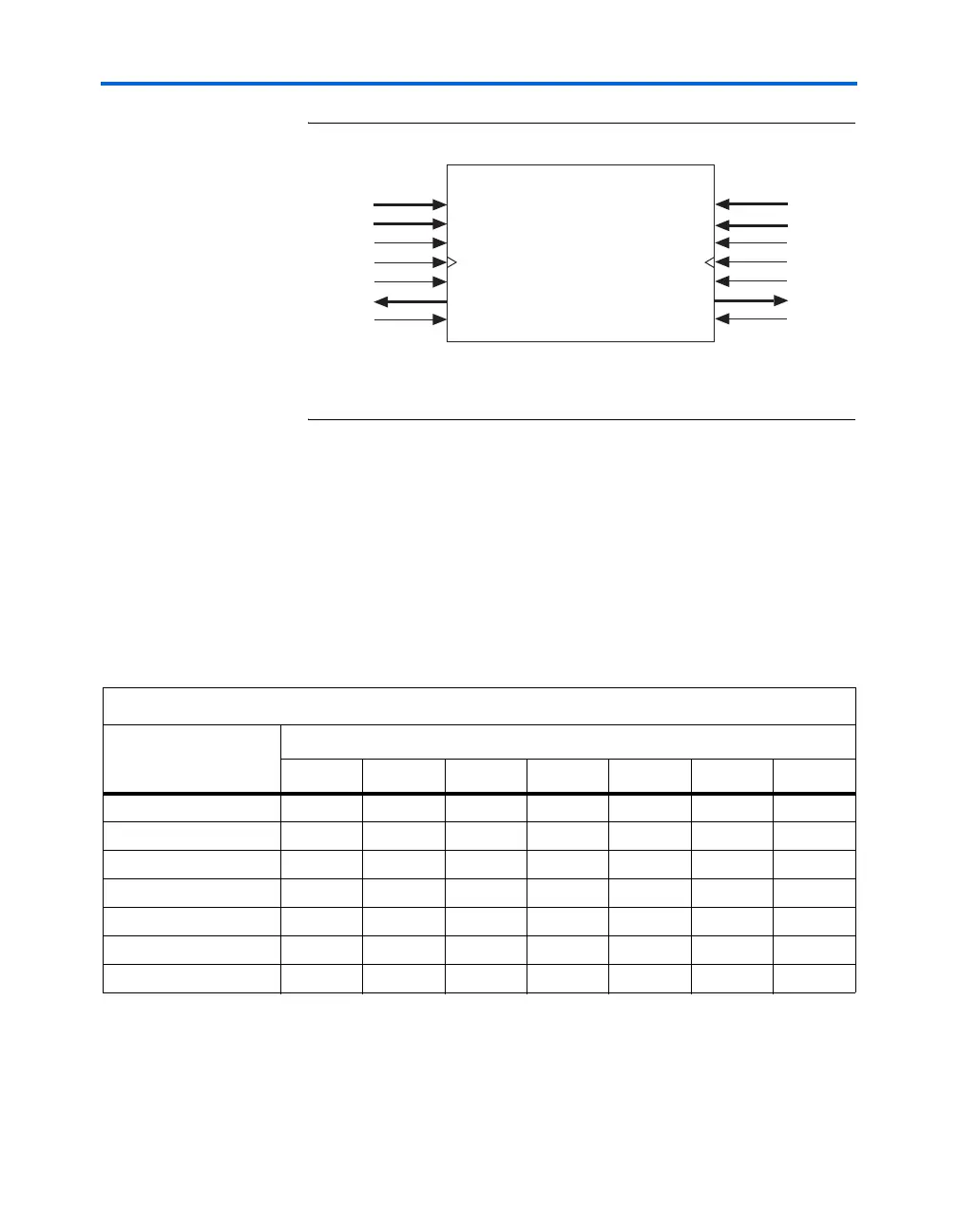

Table 2–10. M4K Block Mixed-Port Width Configurations (True Dual-Port)

Port A

Port B

4K × 12K × 21K × 4 512 × 8 256 × 16 512 × 9 256 × 18

4K × 1

vvvvv

2K × 2

vvvvv

1K × 4

vvvvv

512 × 8

vvvvv

256 × 16

vvvvv

512 × 9

vv

256 × 18

vv

Loading...

Loading...