Section II–2 Altera Corporation

Memory Stratix Device Handbook, Volume 2

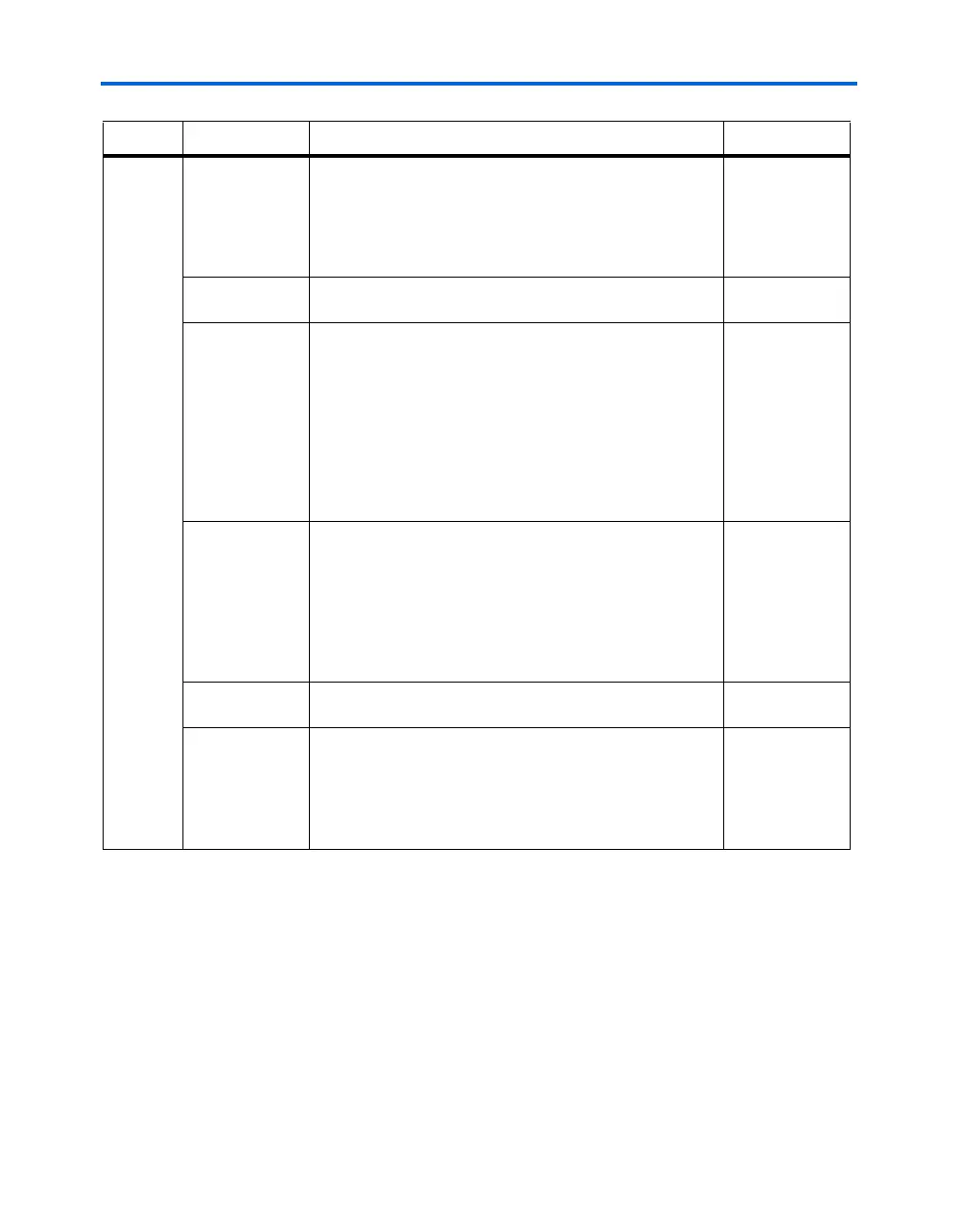

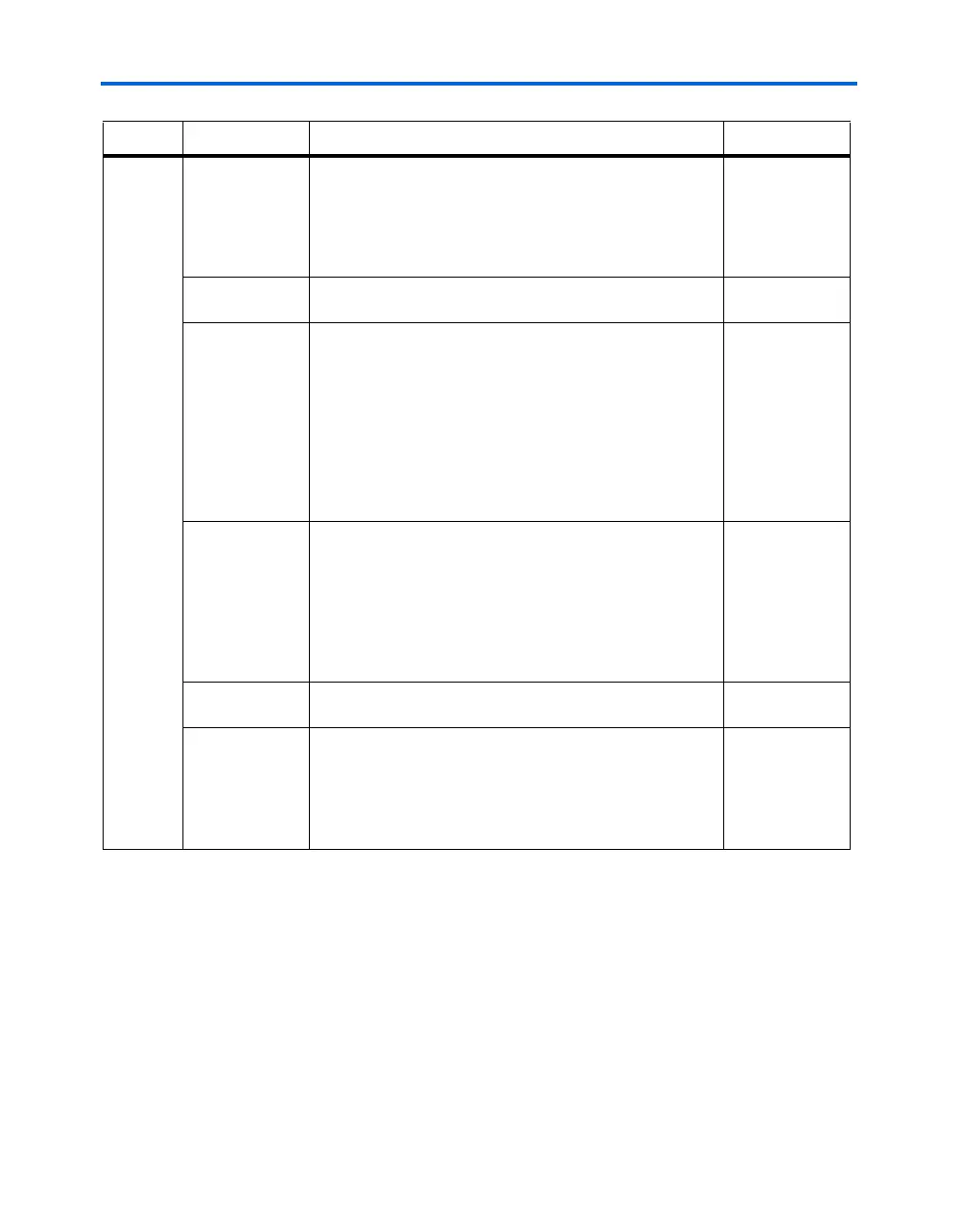

3 June 2006, v3.3 ● Changed the name of the chapter from External Memory

Interfaces to External Memory Interfaces in Stratix &

Stratix GX Devices to reflect its shared status between

those device handbooks.

● Added cross reference regarding frequency limits for 72

and 90

° phase shift for DQS.

July 2005, v3.2

● Updated mathematical symbols in Table 3–3.

● Updated “DQS Phase-Shift Circuitry” section.

September

2004, v3.1

● Moved Figure 8 to become Figure 1, “Example of Where

a DQS Signal is Center-Aligned in the IOE” on page 3–3.

● Updated Table 3–1 on page 3–10, updated Note 4. Note

4, 5, and 6, are now Note 5, 6, and 7, respectively.

● Updated Table 3–2 on page 3–10.

● Updated Table 3–3 on page 3–13.

● Updated Note on page 3–14.

● Moved the “External Memory Standards” on page 3–1 to

follow the Introduction section.

● Moved “Conclusion” on page 3–27 to end of chapter.

April 2004, v3.0

● Chapter renamed Chapter 3, External Memory Interfaces

in Stratix & Stratix GX Devices.

● Table 3–1: DDR SDRAM - side banks row added, ZBT

SRAM row updated.

● Added Tables 3–2 and 3–4.

● DQSn pins removed (page 3-5)

● Deleted “QDR SRAM Interfacing” figure.

● Replaced “t

ZX

& t

XZ

Timing Diagram.”

November 2003,

v2.1

● Removed support for series and parallel on-chip

termination.

July 2003, v2.0

● altddio_bidir function is used for DQS in versions before

Quartus II 3.0. (page 3-2)

● Updated naming convention for DQS pins on page 3-9 to

match pin tables.

● Clarified input clock to PLL must come from an external

input pin on page 3-12.

Chapter Date/Version Changes Made Comments

Loading...

Loading...