Altera Corporation 3–13

June 2006 Stratix Device Handbook, Volume 2

External Memory Interfaces in Stratix & Stratix GX Devices

bottom side of the device are dedicated DQS pins. The DQS2T, DQS7T,

DQS2B, and DQS7B pins are dedicated DQS pins for ×32 mode, and each

group consists of one DQS and 32 DQ pins.

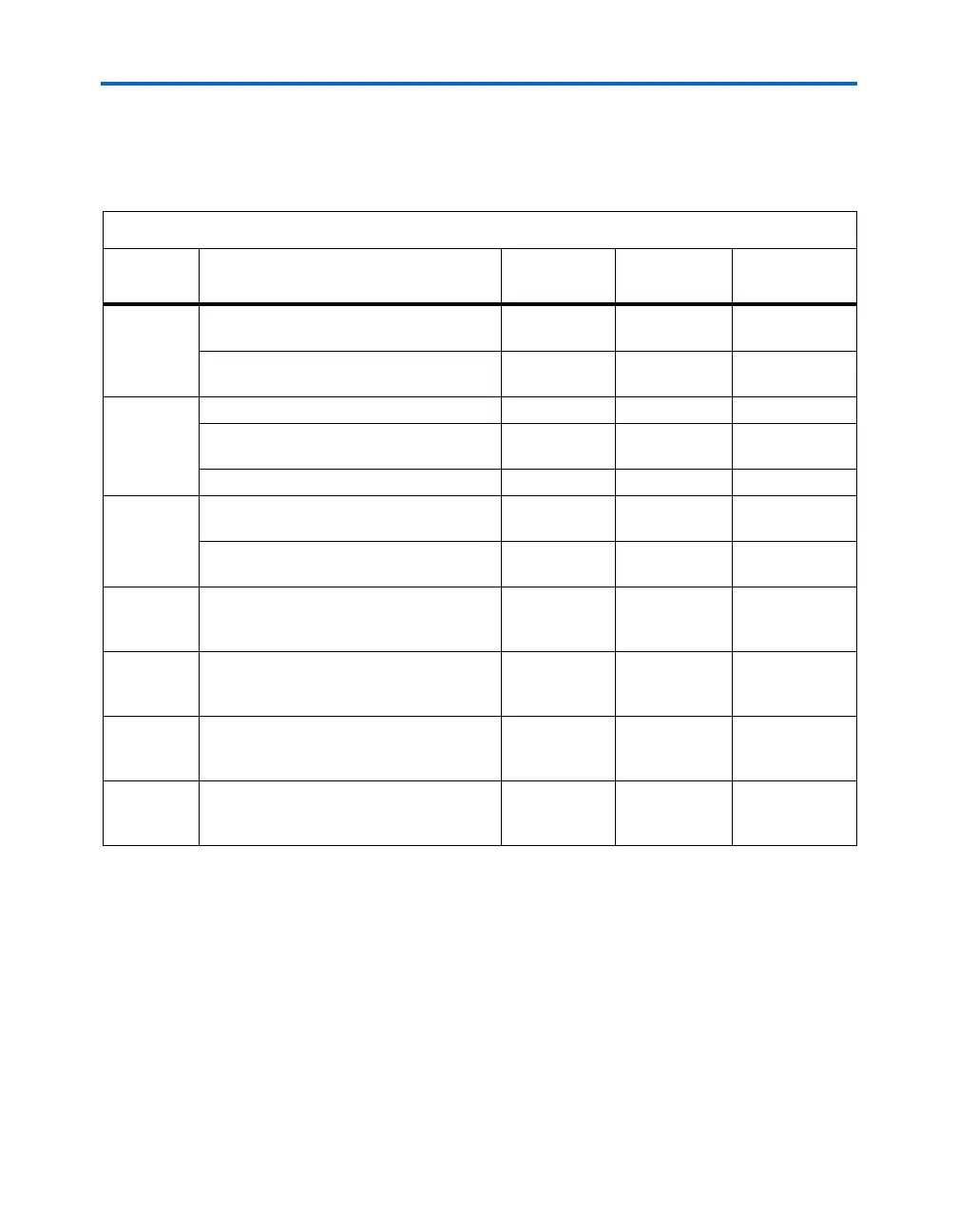

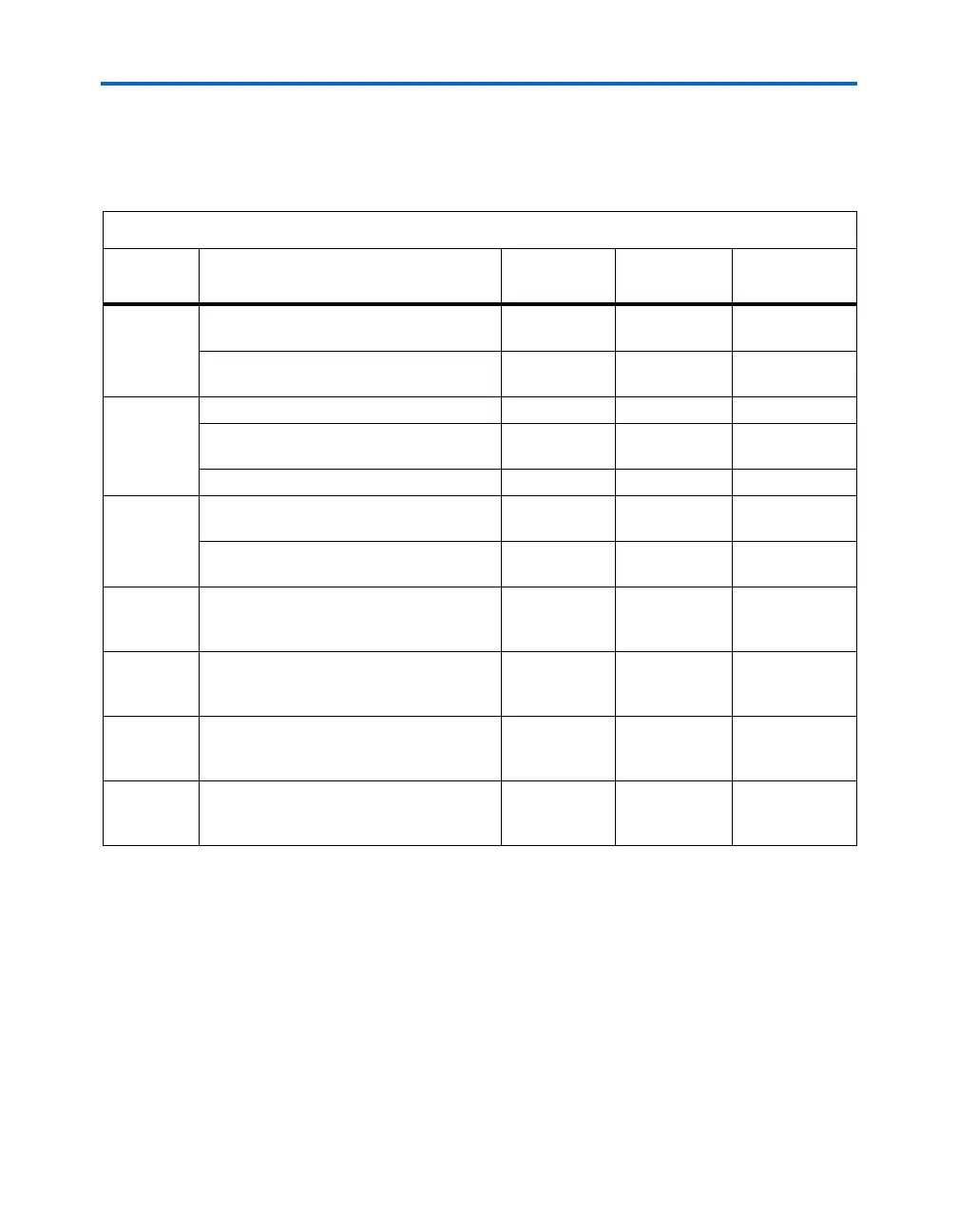

Table 3–3. DQS & DQ Bus Mode Support Note (1)

Device Package

Number of ×8

Groups

Number of ×16

Groups

Number of ×32

Groups

EP1S10 672-pin BGA

672-pin FineLine BGA

®

12 (2) 00

484-pin FineLine BGA

780-pin FineLine BGA

16 (3) 04

EP1S20 484-pin FineLine BGA 18 (4) 7 (5) 4

672-pin BGA

672-pin FineLine BGA

16 (3) 7 (5) 4

780-pin FineLine BGA 20 7 (5) 4

EP1S25 672-pin BGA

672-pin FineLine BGA

16 (3) 84

780-pin FineLine BGA

1,020-pin FineLine BGA

20 8 4

EP1S30 956-pin BGA

780-pin FineLine BGA

1,020-pin FineLine BGA

20 8 4

EP1S40 956-pin BGA

1,020-pin FineLine BGA

1,508-pin FineLine BGA

20 8 4

EP1S60 956-pin BGA

1,020-pin FineLine BGA

1,508-pin FineLine BGA

20 8 4

EP1S80 956-pin BGA

1,508-pin FineLine BGA

1,923-pin FineLine BGA

20 8 4

Notes to Ta b le 3 – 3 :

(1) For V

REF

guidelines, see the Selectable I/O Standards in Stratix & Stratix GX Devices chapter of the Stratix Device

Handbook, Volume 2 or the Stratix GX Handbook, Volume 2.

(2) These packages have six groups in I/O banks 3 and 4 and six groups in I/O banks 7 and 8.

(3) These packages have eight groups in I/O banks 3 and 4 and eight groups in I/O banks 7 and 8.

(4) This package has nine groups in I/O banks 3 and 4 and nine groups in I/O banks 7 and 8.

(5) These packages have three groups in I/O banks 3 and 4 and four groups in I/O banks 7 and 8.

Loading...

Loading...