Altera Corporation 9–11

July 2005 Stratix Device Handbook, Volume 2

Implementing SFI-4 in Stratix & Stratix GX Devices

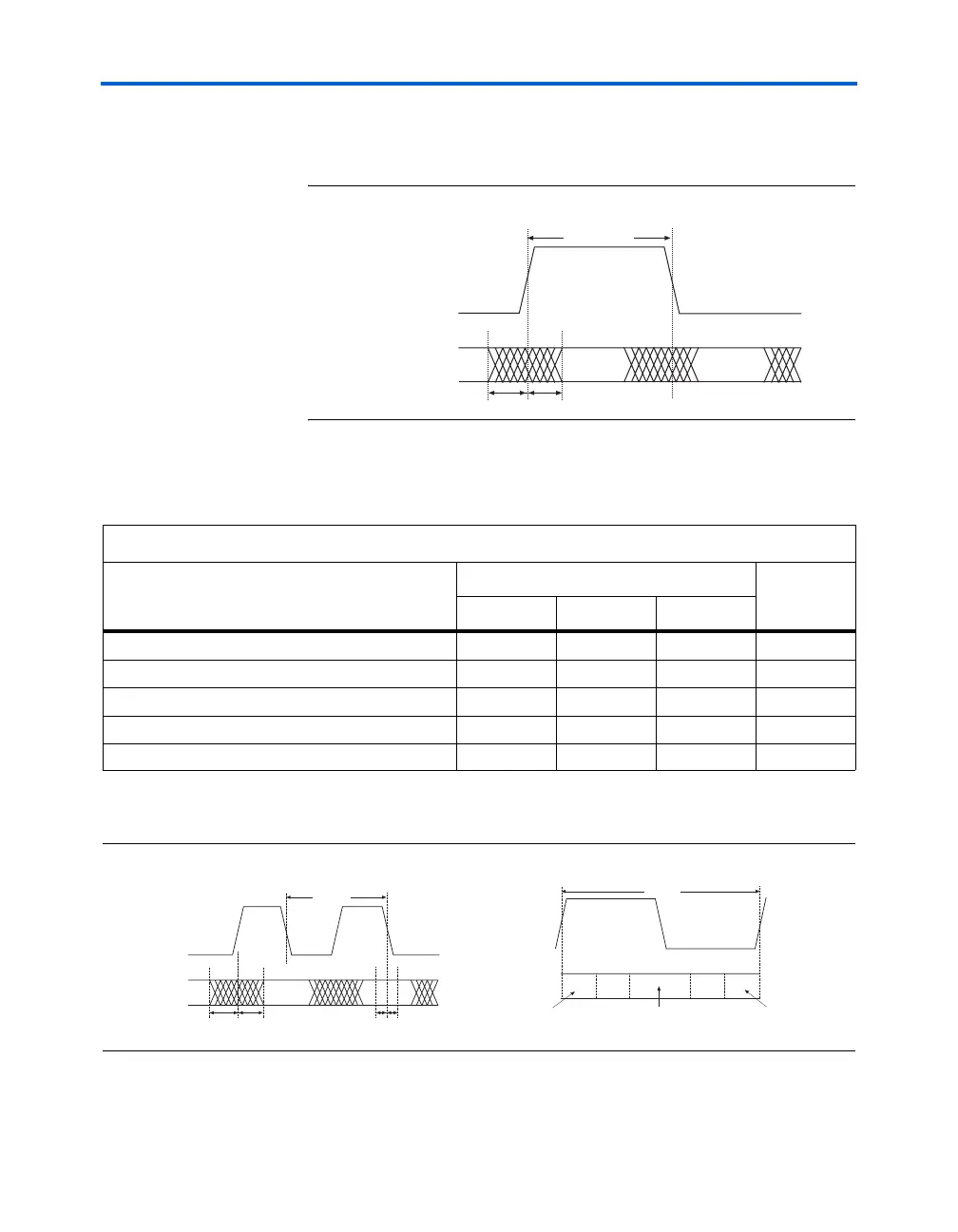

Figure 9–8 shows the timing diagram for the SFI-4 framer transmitter in

× 2 (311 MHz clock) mode

Figure 9–8. Framer Transmitter × 2 (311 MHz Clock) Mode Timing Diagram

Table 9–5 lists the timing specifications for the SFI-4 framer transmitter in

× 2 (311 MHz clock) mode.

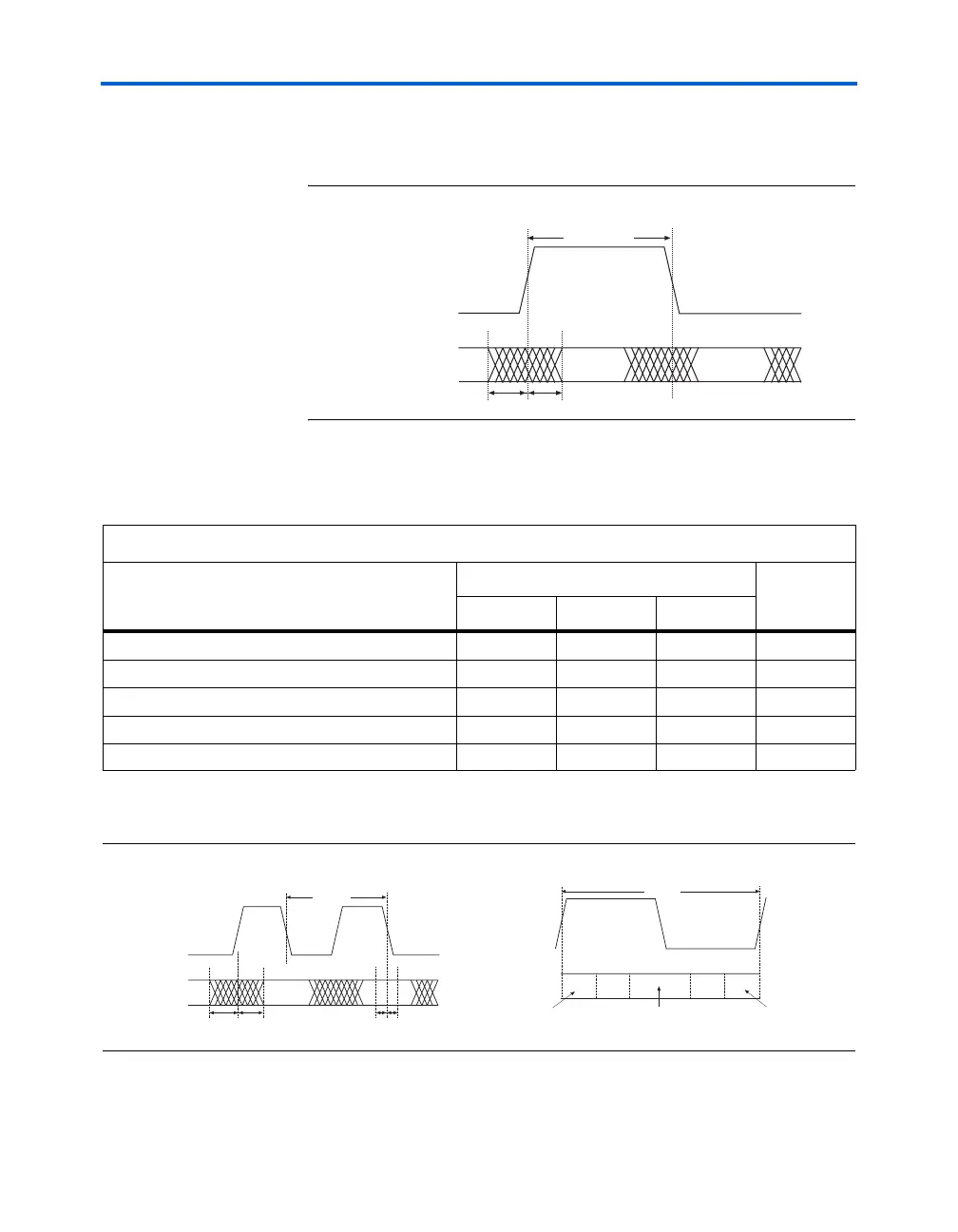

Figure 9–9 shows the timing diagram for the SFI-4 framer receiver.

Figure 9–9. Framer Receiver Timing Diagram

T

period/2

T

cq_pre

T

cq_post

Valid

Data

TX_DATA[15..0]

Valid

Data

TX_CLK(P)

Table 9–5. SFI-4 Framer Transmitter × 2 (311 MHz Clock) Mode Timing Specifications

Parameter

Value

Unit

Min Typ Max

TX_CLK (T

period

)

3,215 ps

Data invalid window before the rising edge (T

cq_pre

)200ps

Data invalid window after the rising edge (T

cq_post

)200ps

TX_CLK duty cycle

48 52 %

Framer transmitter channel-to-channel skew 200 ps

T

period

T

cq_pre

T

cq_post

T

setup

T

hold

Valid

Data

RX_DATA[15..0]

RX_CLK(P)

RX_CLK(P)

RSKM

Sampling Window

RSKM

Transmitter Channel-to-Channel

Skew/2

Transmitter Channel-to-Channel

Skew/2

Tperiod

RX_DATA[15..0]

Loading...

Loading...