1–42 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Clocking

Input clocks for fast PLLs 1, 2, 3, and 4 come from CLK pins. Stratix GX

devices use PLLs 3 and 4 in the HSSI block only. A multiplexer chooses

one of two possible CLK pins to drive each PLL. This multiplexer is not a

clock switchover multiplexer and is only used for clock input

connectivity.

Either a FPLLCLK input pin or a CLK pin can drive the fast PLLs in the

corners (7, 8, 9, and 10) when used for general purpose. CLK pins cannot

drive these fast PLLs in high-speed differential I/O mode. PLLs 9 and 10

are used for the HSSI block in Stratix GX devices and are not available.

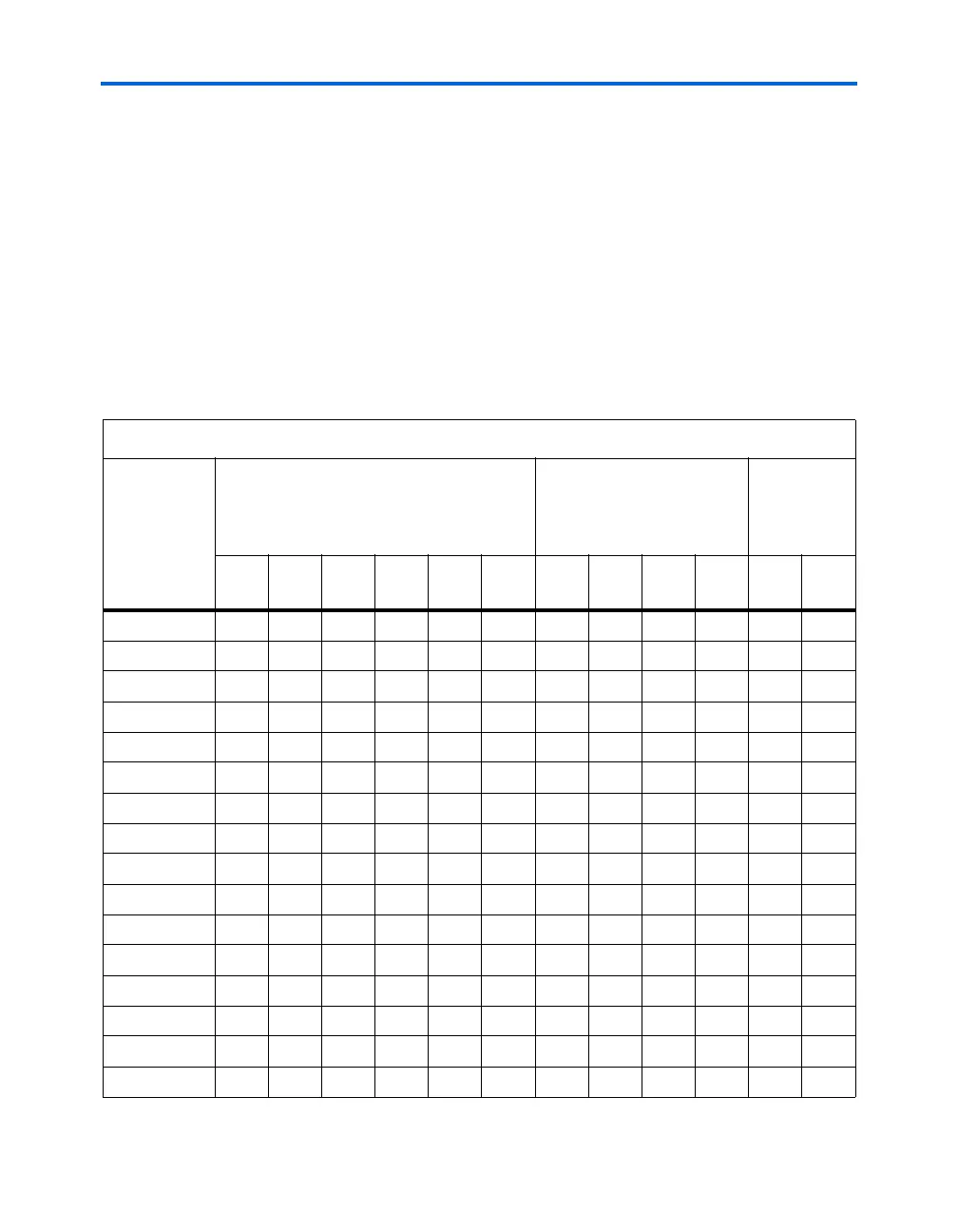

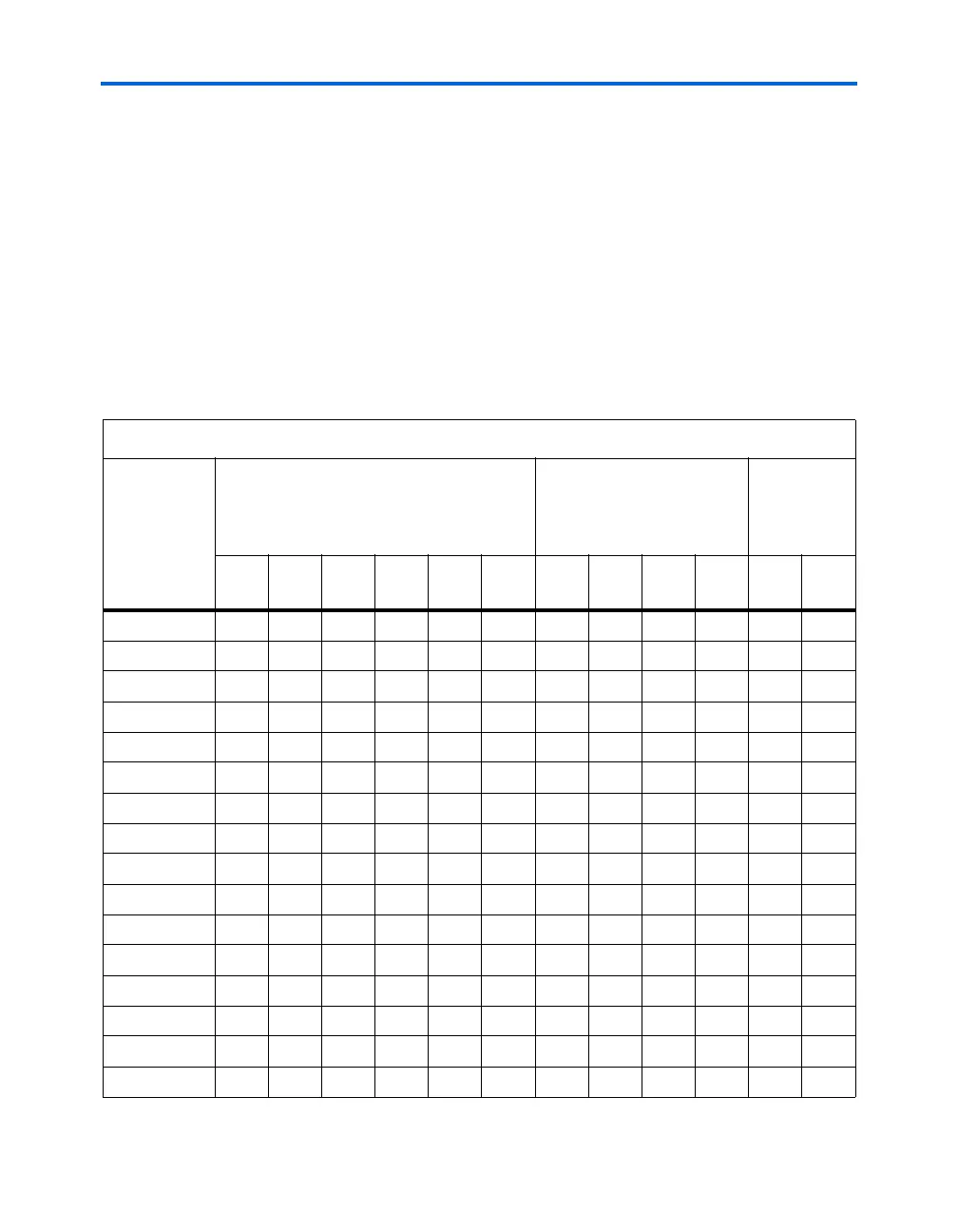

Table 1–14 shows which PLLs are available for each Stratix device and

which input clock pin drives which PLLs.

Table 1–14. Stratix Clock Input Sources For Enhanced & Fast PLLs (Part 1 of 2)

Clock Input

Pins

All Stratix Devices

EP1S30, EP1S40, EP1S60 &

EP1S80 Devices Only

EP1S40 (3),

EP1S60 &

EP1S80

Devices Only

PLL 1

(1)

PLL 2

(1)

PLL 3

(1)

PLL 4

(1)

PLL 5

(2)

PLL 6

(2)

PLL 7

(1)

PLL 8

(1)

PLL 9

(1)

PLL

10 (1)

PLL

11 (2)

PLL

12 (2)

CLK0p/n

vv

CLK1p/n

v

CLK2p/n

vv

CLK3p/n

v

CLK4p/n

v

CLK5p/n

v

CLK6p/n

v

CLK7p/n

v

CLK8p/n

vv

CLK9p/n

v

CLK10p/n

vv

CLK11p/n

v

CLK12p/n

v

CLK13p/n

v

CLK14p/n

v

CLK15p/n

v

Loading...

Loading...