1–6 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Enhanced PLLs

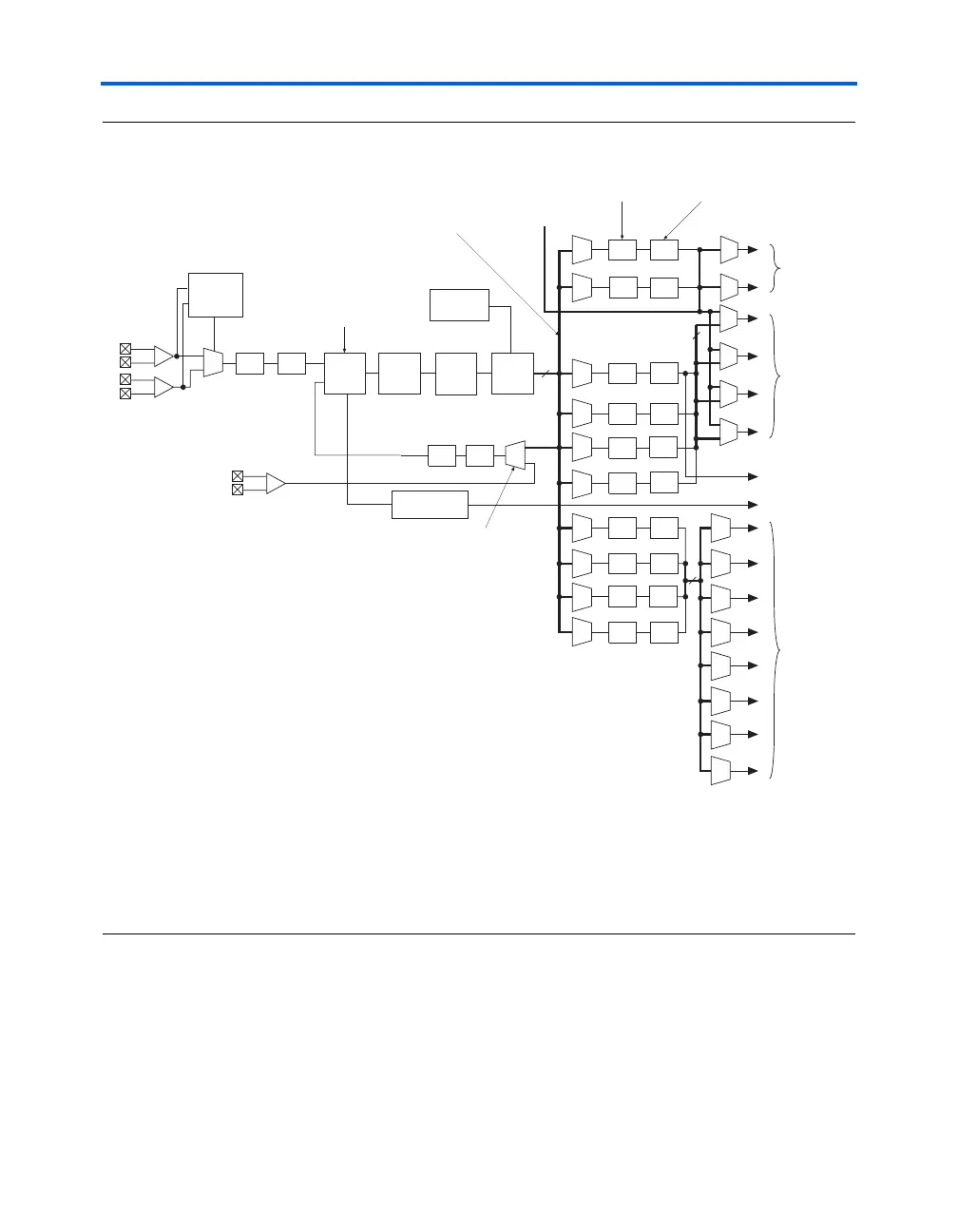

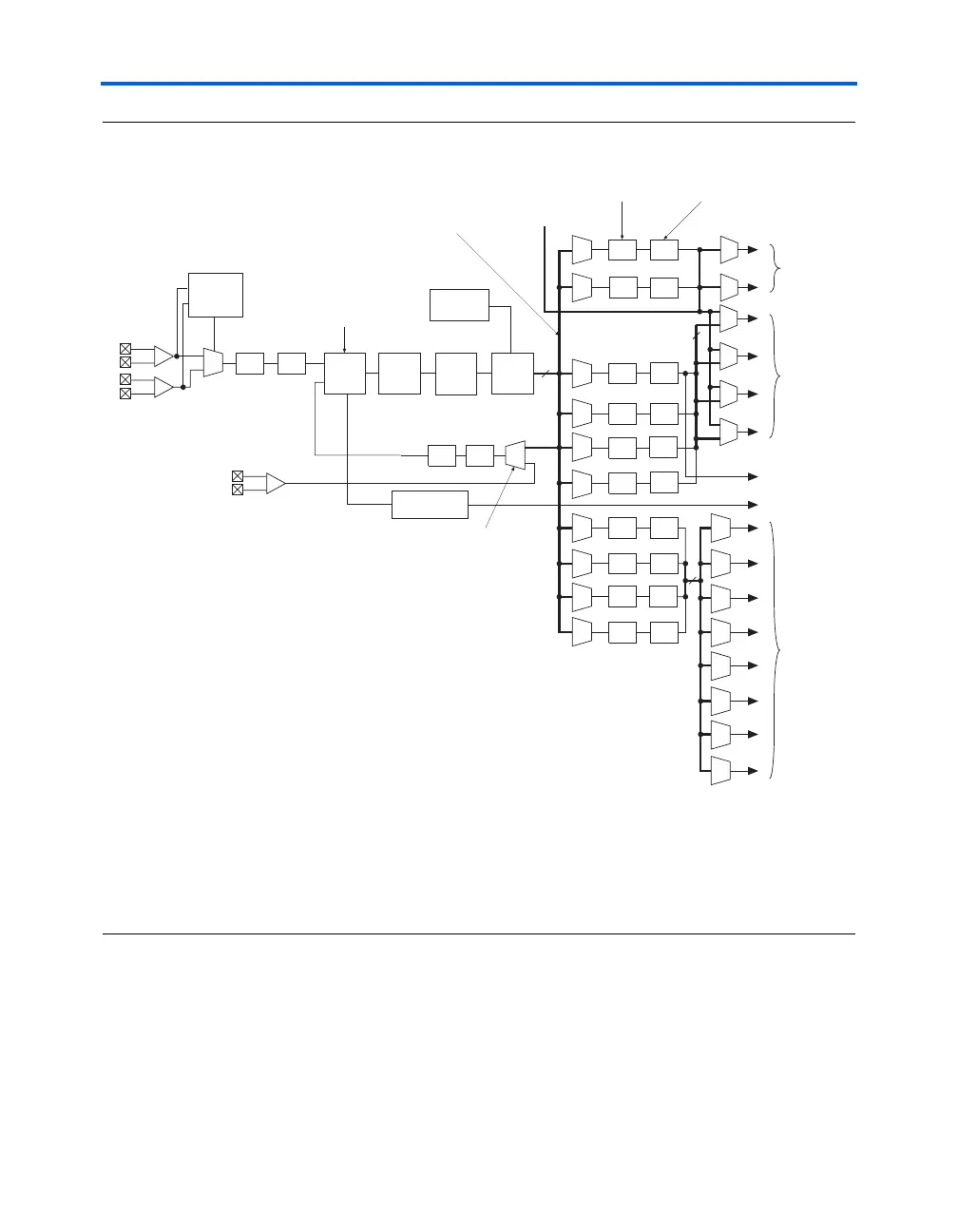

Figure 1–3. Stratix & Stratix GX Enhanced PLL

Notes to Figure 1–3:

(1) External feedback is available in PLLs 5 and 6.

(2) This single-ended external output is available from the g0 counter for PLLs 11 and 12.

(3) These four counters and external outputs are available in PLLs 5 and 6.

(4) This connection is only available on EP1SGX40 Stratix GX devices and EP1S40 and larger Stratix devices. For

example, PLLs 5 and 11 are adjacent and PLLs 6 and 12 are adjacent. The EP1S40 device in the F780 package does

not support PLLs 11 and 12.

÷

n

Charge

Pump

VCO

÷

g

0

÷

g

1

÷

g

2

÷

e

0

8

4

Global

Clocks

÷

e

1

÷

e

2

I/O Buffers (3)

÷

e

3

Δt

Δt

Δt

Δt

Δt

Δt

Δt

Δt

Lock Detect

to I/O or general

routing

INCLK0

INCLK1

FBIN

÷

g

3

÷

l

1

÷

l

0

From Adjacent PLL (4)

÷

m

Spread

Spectrum

I/O Buffers

(2)

(1)

Loop

Filter

& Filter

Programmable

Time Delay on

Each PLL Port

Post-Scale

Counters

Clock

Switch-Over

Circuitry

Phase Frequency

Detector (PFD)

VCO Phase Selection

Selectable at Each

PLL Output Port

VCO Phase Selection

Affecting All Outputs

Δt

Δt

Δt

n

Δt

m

Regional

Clocks

4

Loading...

Loading...