Altera Corporation 1–7

July 2005 Stratix Device Handbook, Volume 2

General-Purpose PLLs in Stratix & Stratix GX Devices

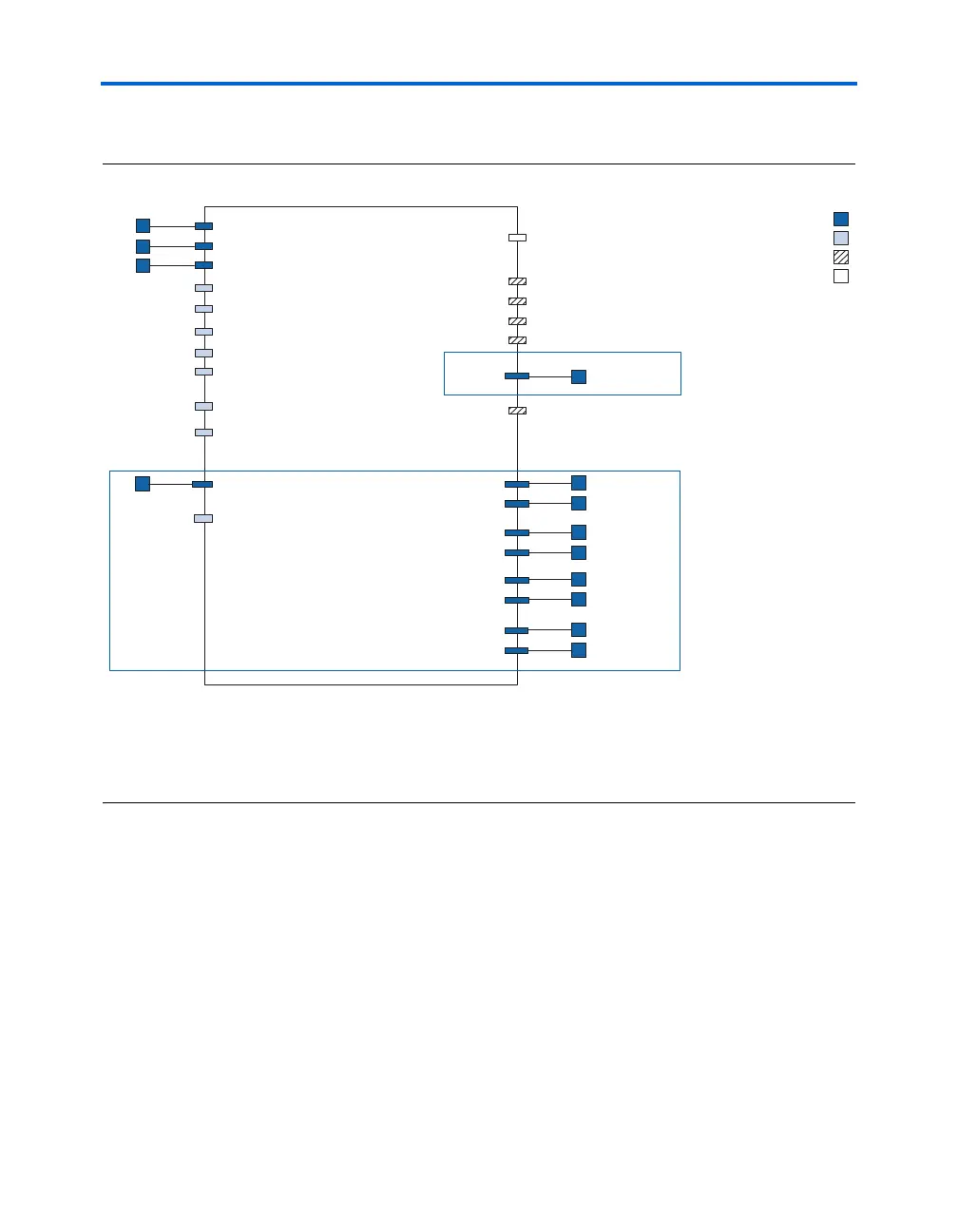

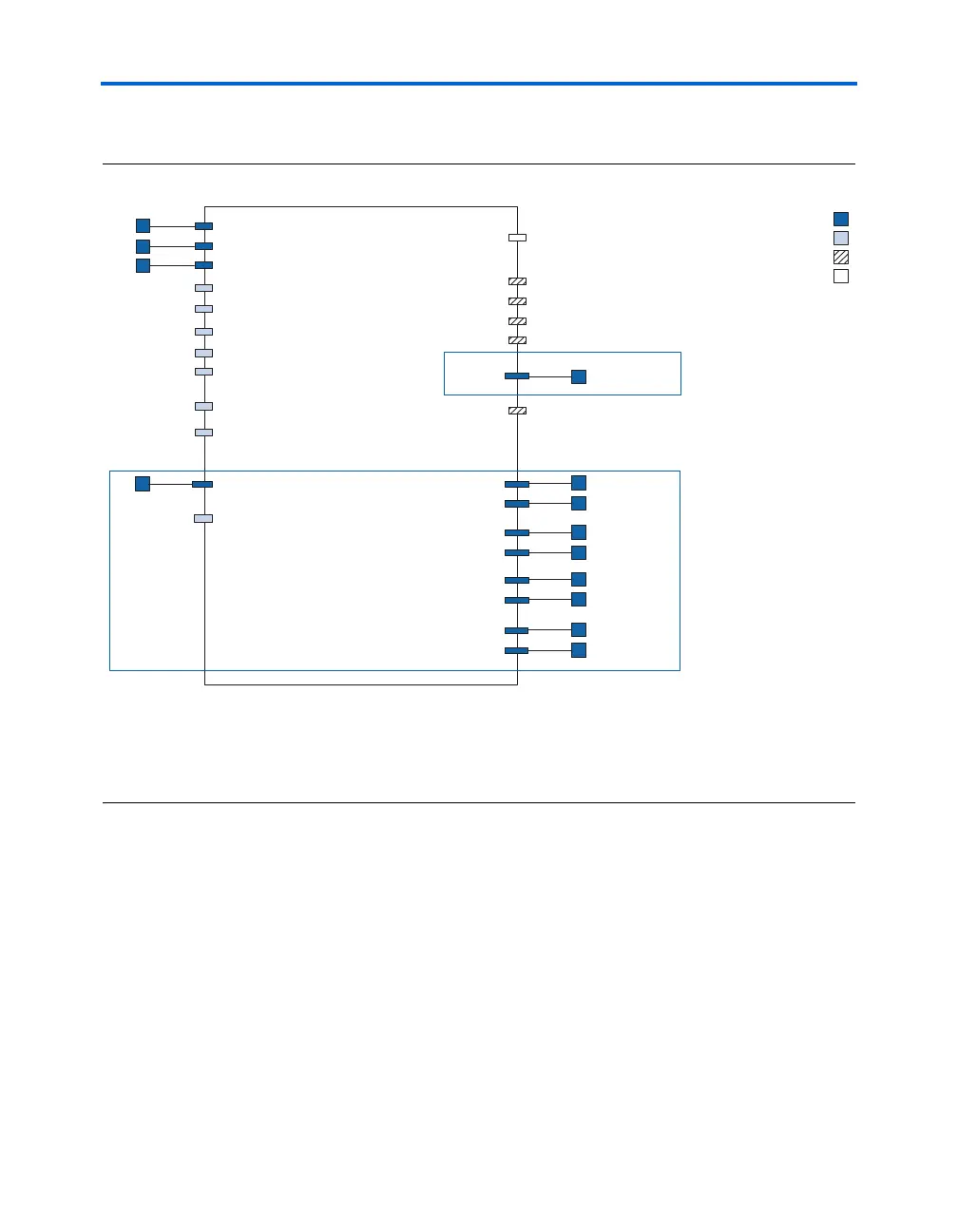

Figure 1–4 shows all the possible ports of the enhanced PLLs.

Figure 1–4. Enhanced PLL Signals

Notes to Figure 1–4:

(1) This input pin is shared by all enhanced and fast PLLs.

(2) These are either single-ended or differential pins.

(3) EP1S10, EP1S20, and EP1S25 devices in 672-pin ball grid array (BGA) and 484- and 672-pin FineLine BGA packages

only have two pairs of external clocks (i.e., pll_out0p, pll_out0n, pll_out1p, and pll_out1n).

inclk0

inclk1

clkswitch

scandata

scanclk

pllenable

clk[5..0]

locked

Physical Pin

clkloss

areset

clkena[5..0]

pfdena

Signal Driven by Internal Logic

Signal Driven to Internal Logic

Internal Clock Signal

extclk4

active_clock

extclkena[3..0]

pll_out0p

fbin

Only PLLs

5 and 6

clkbad[1..0]

(1)

(2)

(2)

pll_out0n

pll_out1p

pll_out1n

pll_out2p

pll_out2n

pll_out3p

pll_out3n

scanaclr

(2)

Only PLLs

11 and 12

scandataout

(3)

(3)

(3)

(3)

Loading...

Loading...