1–8 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Enhanced PLLs

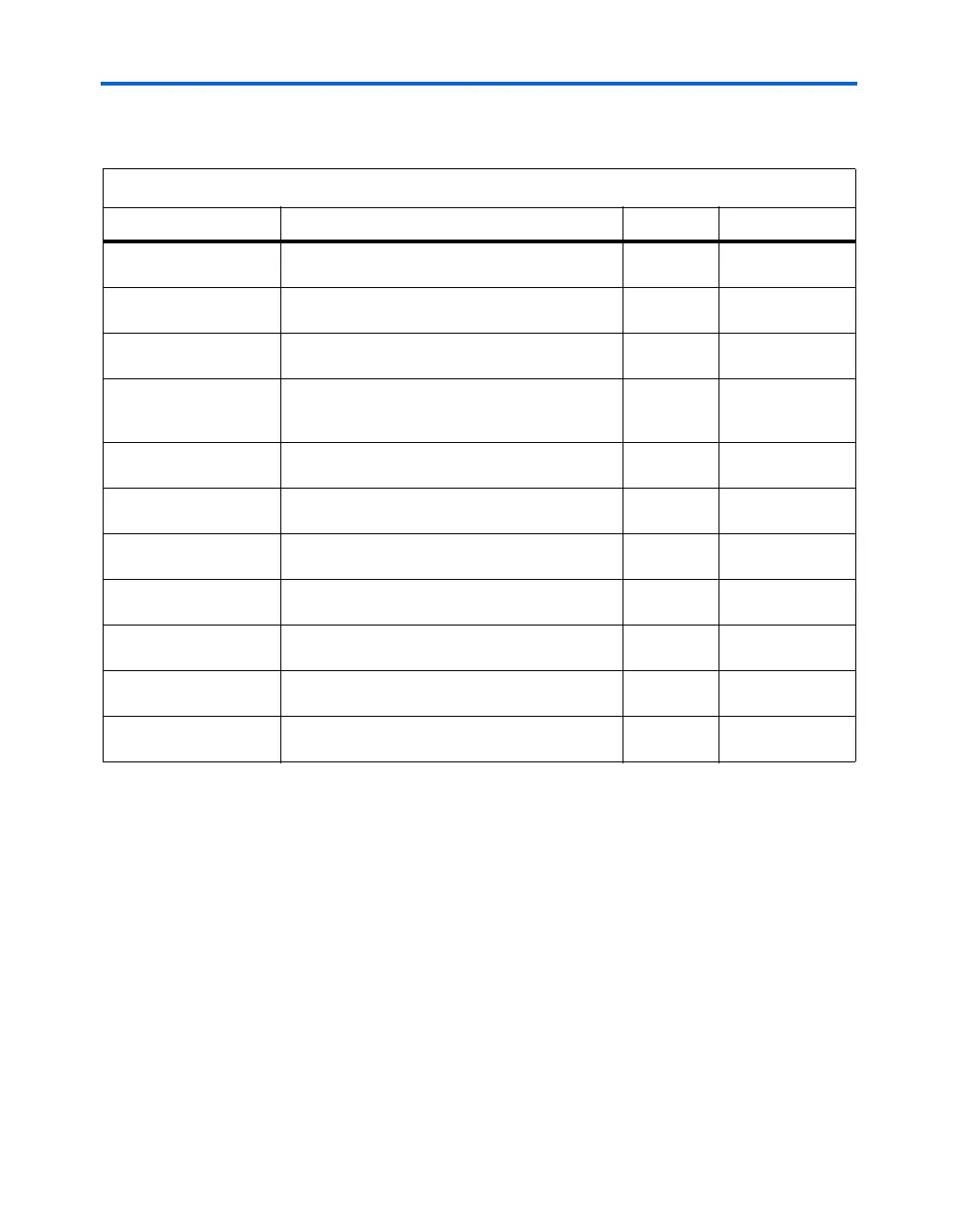

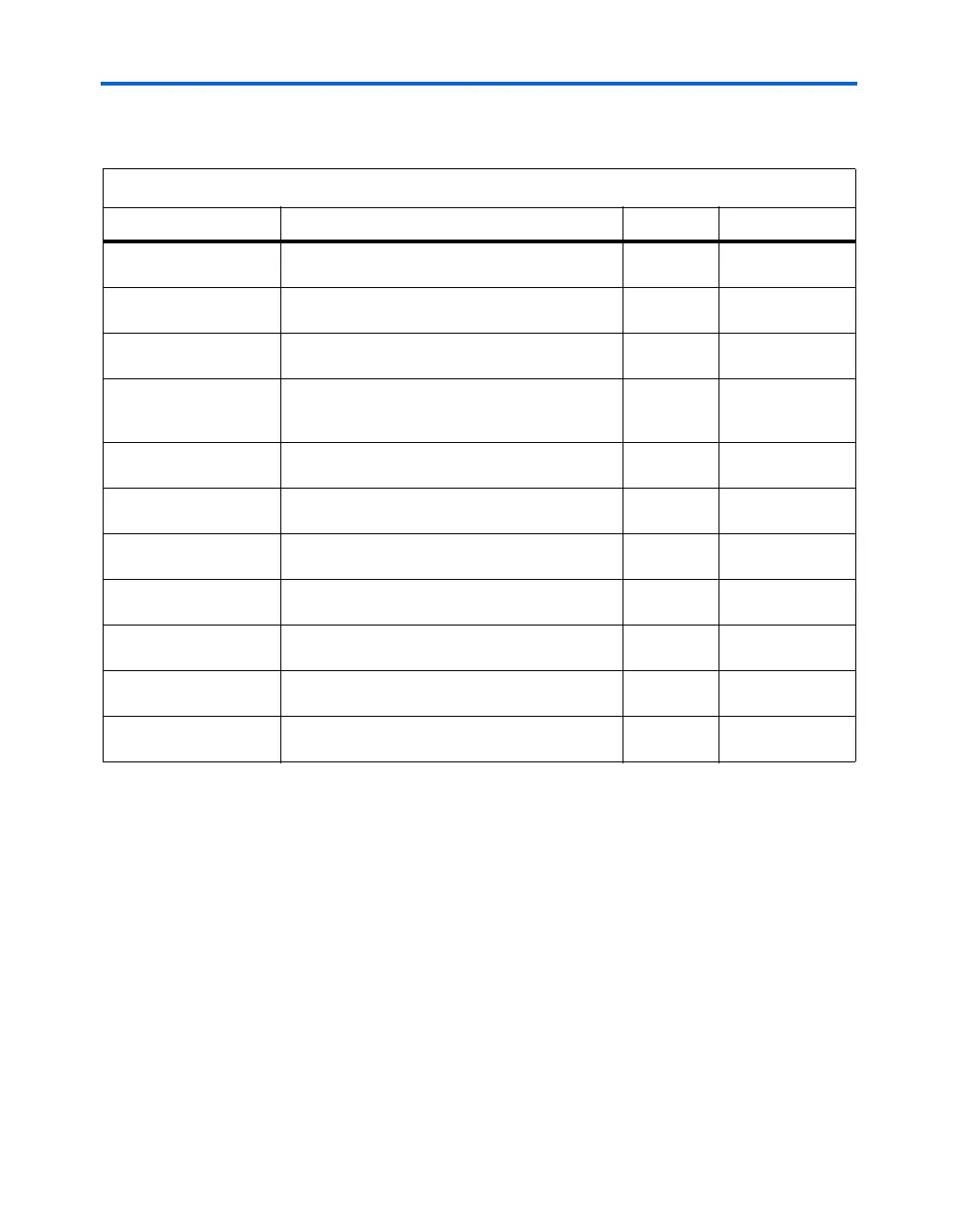

Tables 1–4 and 1–5 describe all the enhanced PLL ports.

Table 1–4. Enhanced PLL Input Signals

Port Description Source Destination

inclk[1..0]

Primary and secondary reference clock inputs to

PLL

Pin ×n counter

fbin

External feedback input to the PLL (PLLs 5 and 6

only)

Pin Phase frequency

detector (PFD)

pllena

Enable pin for enabling or disabling all or a set of

PLLs⎯active high

Pin General PLL

control signal

clkswitch

Switchover signal used to initiate external clock

switchover control⎯this signal switches the clock

on the rising edge of clkswitch

Logic array PLL switchover

circuit

areset

Signal used to reset the PLL which re-

synchronizes all the counter outputs⎯active high

Logic array General PLL

control signal

clkena[5..0]

Enable clock driving regional or global

clock⎯active high

Logic array Clock output

extclkena[3..0]

Enable clock driving external clock (PLLs 5 and 6

only)⎯active high

Logic array Clock output

pfdena

Enables the outputs from the phase frequency

detector⎯active high

Logic array PFD

scanclk

Serial clock signal for the real-time PLL control

feature

Logic array Reconfiguration

circuit

scandata

Serial input data stream for the real-time PLL

control feature

Logic array Reconfiguration

circuit

scanaclr

Serial shift register reset clearing all registers in

the serial shift chain⎯active high

Logic array Reconfiguration

circuit

Loading...

Loading...