8–4 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

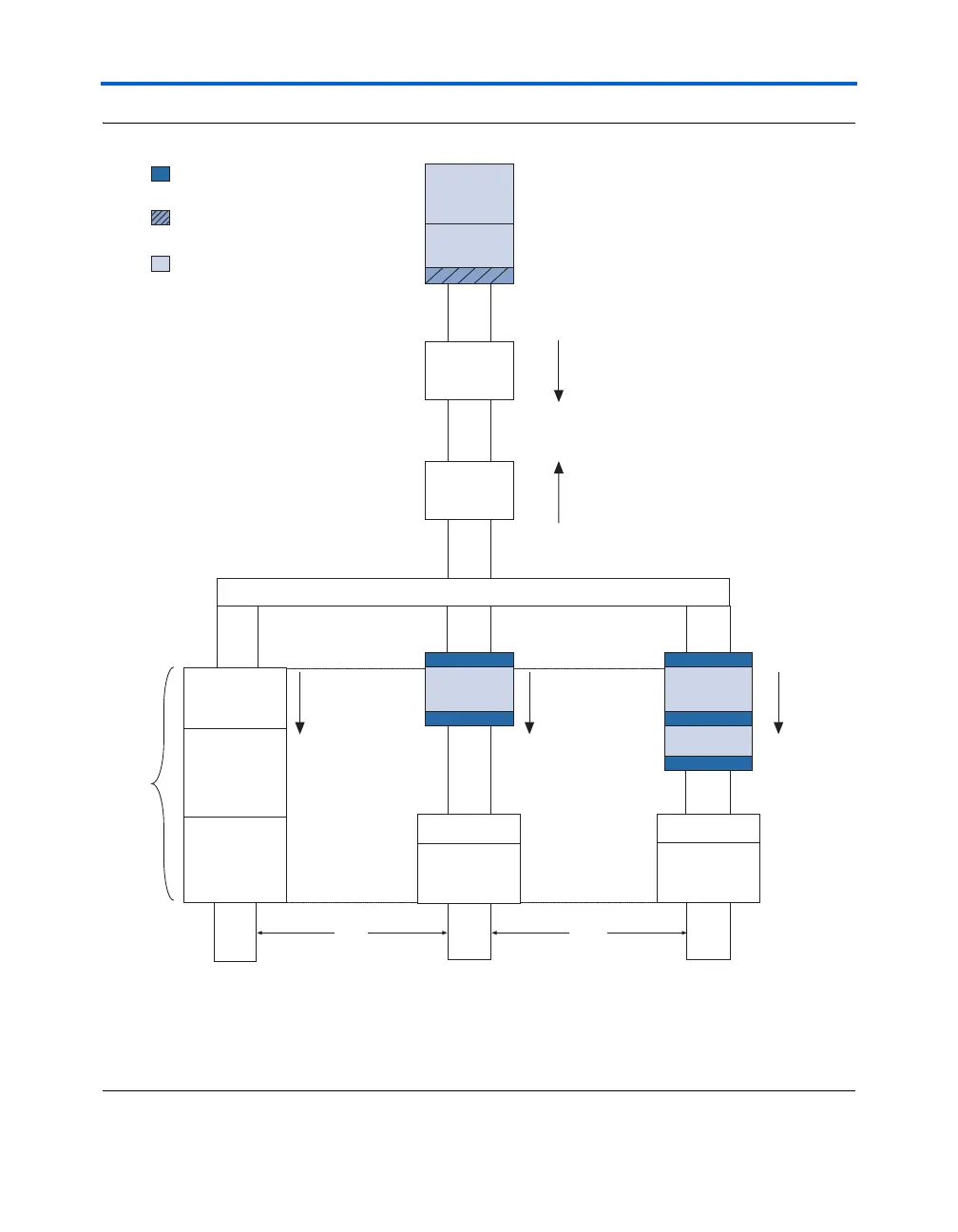

10-Gigabit Ethernet

Figure 8–2. 10-Gigabit Ethernet Block Diagram

Notes to Figure 8–2:

(1) The reconciliation sublayer (RS) interfaces the serial MAC data stream and the parallel data of XGMII.

(2) The XGMII extender sublayer (XGXS) extends the distance of XGMII when used with XUAI and provides the data

conversion between XGMII and XAUI.

(3) The WAN interface sublayer (WIS) implements the OC-192 framing and scrambling functions.

PCS

PMA

PCS

PMA

WIS (3)

10GBASE-R 10GBASE-W

XGMII (32 Bits at 156.25 Mbps DDR 1.5-V HSTL)

MAC

RS (1)

XGXS (2)

8b/10b

XAUI (4 Bits at 3.125 Gbps PCML)

XGMII (32 Bits at 156.25 Mbps DDR 1.5-V HSTL)

8b/10b

PHY

MDI

10GBASE-X

64b/66b8B/10B

XSBI (16 Bits at

622.08 Mbps LVDS)

64b/66b

OC-192 Framing

Interface directly covered in this

application note

Interface indirectly covered in this

application note

Can be implemented in Altera PLDs

XGXS

PCS

MDI

XSBI (16 Bits at

644.5 Mbps LVDS)

PMD

PMD

PMA

PMD

Loading...

Loading...