Altera Corporation 5–57

July 2005 Stratix Device Handbook, Volume 2

High-Speed Differential I/O Interfaces in Stratix Devices

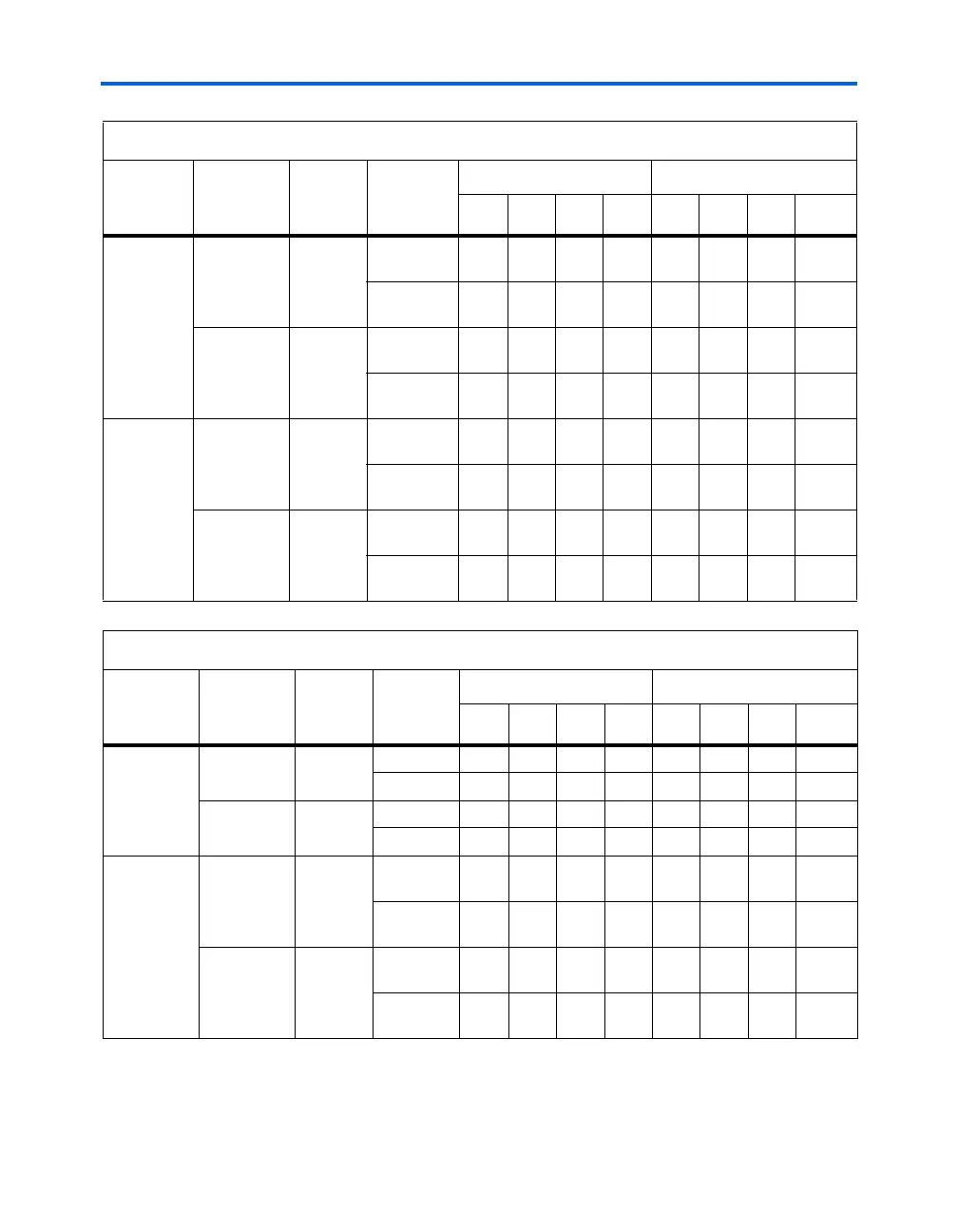

1,020-pin

FineLine

BGA

Transmitter

(4)

80 (10)

(7)

840 18

(2)

17

(3)

17

(3)

18

(2)

20 20 20 20

840 (5)

, (8)

35

(5)

35

(5)

35

(5)

35

(5)

20 20 20 20

Receiver

80 (10)

(7)

840 20 20 20 20 18

(2)

17

(3)

17

(3)

18 (2)

840 (5)

, (8)

40 40 40 40 18

(2)

17

(3)

17

(3)

18 (2)

1,508-pin

FineLine

BGA

Transmitter

(4)

80 (10)

(7)

840 18

(2)

17

(3)

17

(3)

18

(2)

20 20 20 20

840 (5)

, (8)

35

(5)

35

(5)

35

(5)

35

(5)

20 20 20 20

Receiver 80 (10)

(7)

840 20 20 20 20 18

(2)

17

(3)

17

(3)

18 (2)

840 (5)

, (8)

40 40 40 40 18

(2)

17

(3)

17

(3)

18 (2)

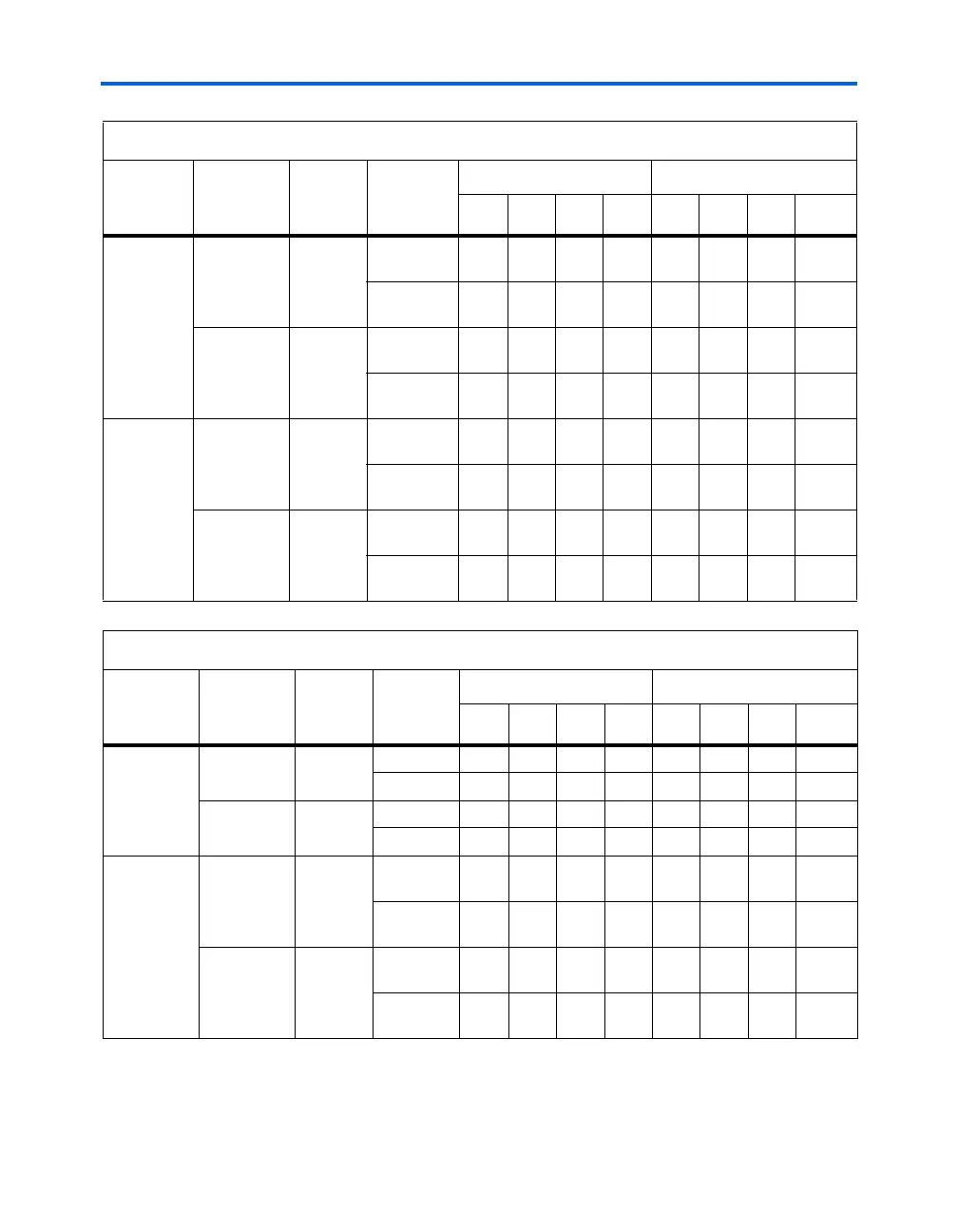

Table 5–13. EP1S60 Differential Channels (Part 1 of 2) Note (1)

Package

Transmitter

/Receiver

Total

Channels

Maximum

Speed

(Mbps)

Center Fast PLLs Corner Fast PLLs (2), (3)

PLL1 PLL2 PLL3 PLL4 PLL7 PLL8 PLL9 PLL10

956-pin

FineLine

BGA

Transmitter

(4)

80 840 12 10 10 12 20 20 20 20

840 (5)

, (8)

22 22 22 22 20 20 20 20

Receiver 80 840 20 20 20 20 12 10 10 12

840 (5)

, (8)

40 40 40 40 12 10 10 12

1,020-pin

FineLine

BGA

Transmitter

(4)

80 (12)

(7)

840 12

(2)

10

(4)

10

(4)

12

(2)

20 20 20 20

840 (5)

, (8)

22

(6)

22

(6)

22

(6)

22

(6)

20 20 20 20

Receiver 80 (10)

(7)

840 20 20 20 20 12

(8)

10

(10)

10

(10)

12 (8)

840 (5)

, (8)

40 40 40 40 12

(8)

10

(10)

10

(10)

12 (8)

Table 5–12. EP1S40 Differential Channels (Part 2 of 2) Note (1)

Package

Transmitter

/Receiver

Total

Channels

Maximum

Speed

(Mbps)

Center Fast PLLs Corner Fast PLLs (2), (3)

PLL1 PLL2 PLL3 PLL4 PLL7 PLL8 PLL9 PLL10

Loading...

Loading...