7–26 Altera Corporation

Stratix Device Handbook, Volume 2 September 2004

Finite Impulse Response (FIR) Filters

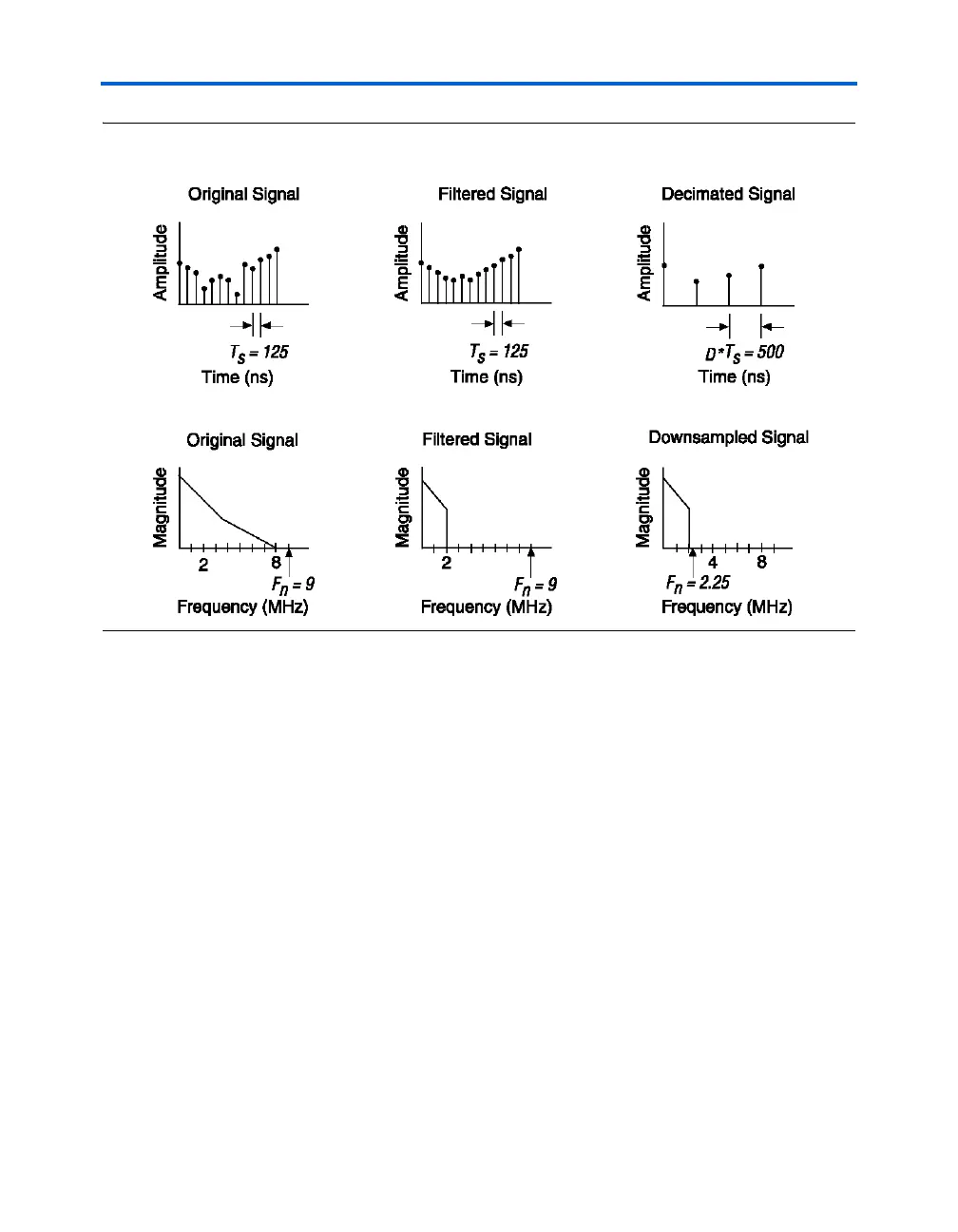

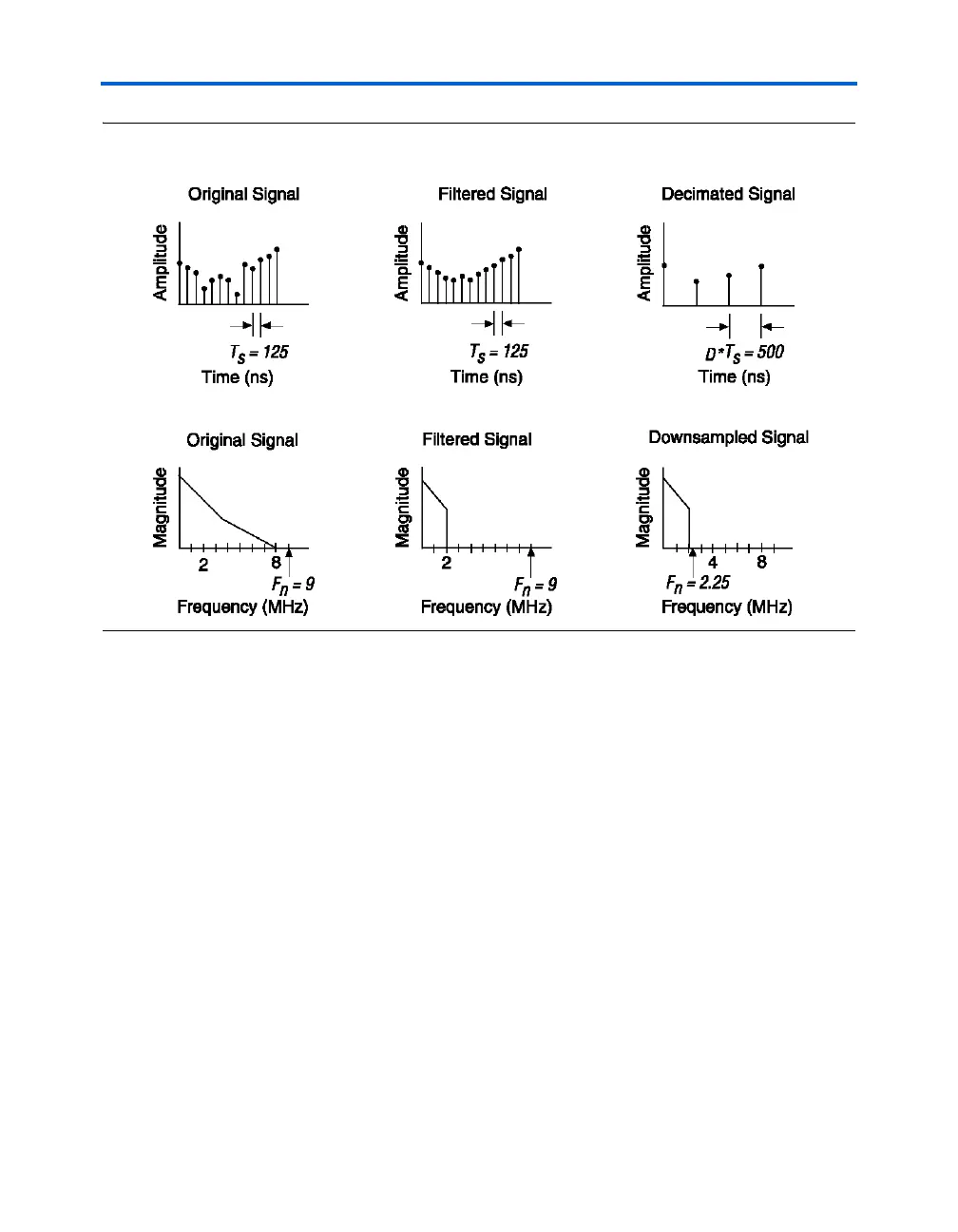

Figure 7–15. Time & Frequency Domain Representations of Decimation for D=4

Polyphase Decimation Filters

Figure 7–14 shows a direct implementation of a decimation filter, which

imposes a high computational burden. For example, if the filter is 16 taps

long and a multiplication takes one cycle, the number of computations

required per cycle is 16× D. Depending on the decimation factor (D), this

number can be quite big and may not be achievable in hardware. A

polyphase implementation of the low pass filter can reduce the number

of computations required, often by a large ratio, as will be evident later in

this section.

The polyphase implementation “splits” the original filter into D

polyphase filters with impulse responses defined by the following

equation.

h

k

n() hk nD+()=

Loading...

Loading...