Altera Corporation 5–29

July 2005 Stratix Device Handbook, Volume 2

High-Speed Differential I/O Interfaces in Stratix Devices

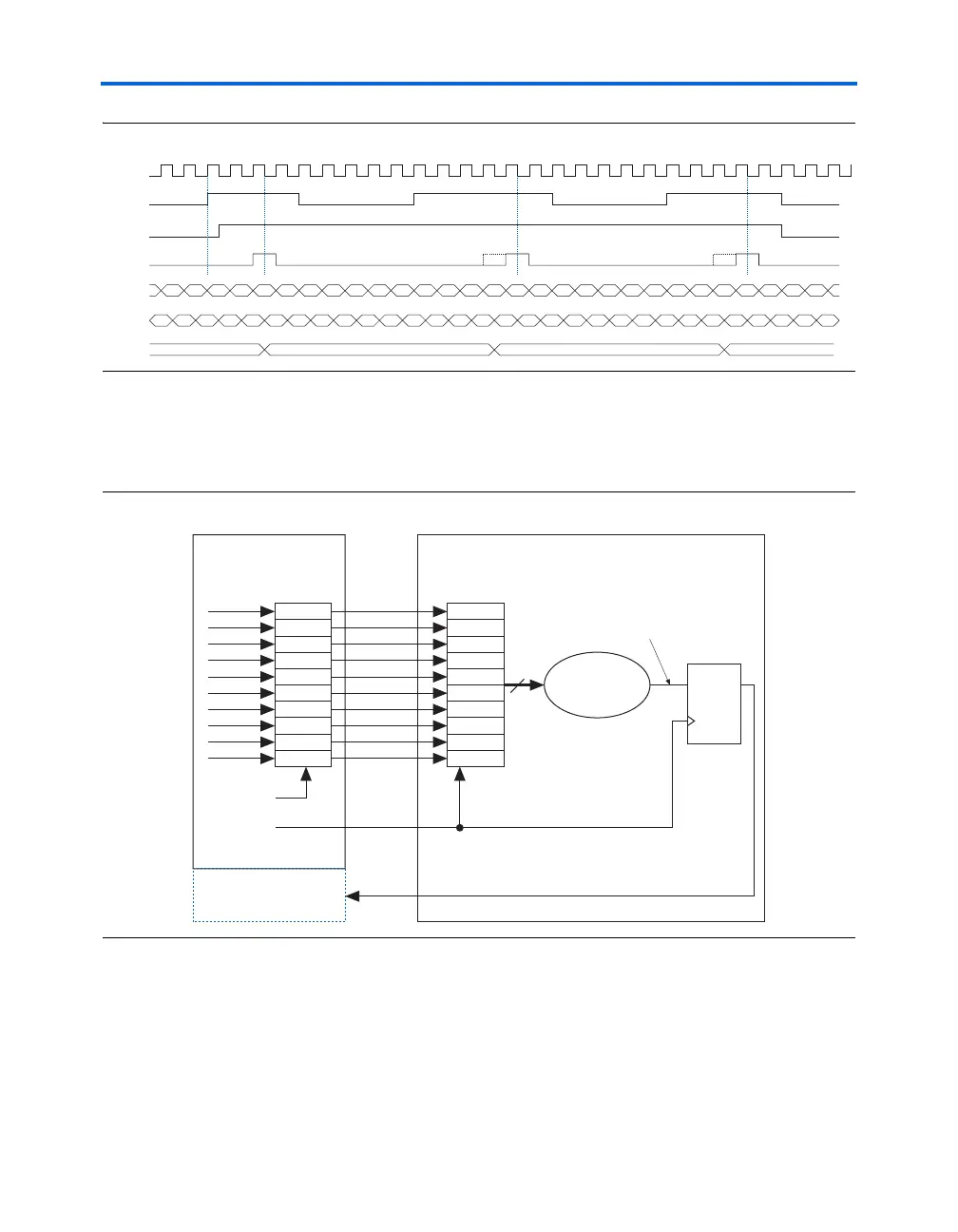

Figure 5–21. Realignment by rx_data_align Node End

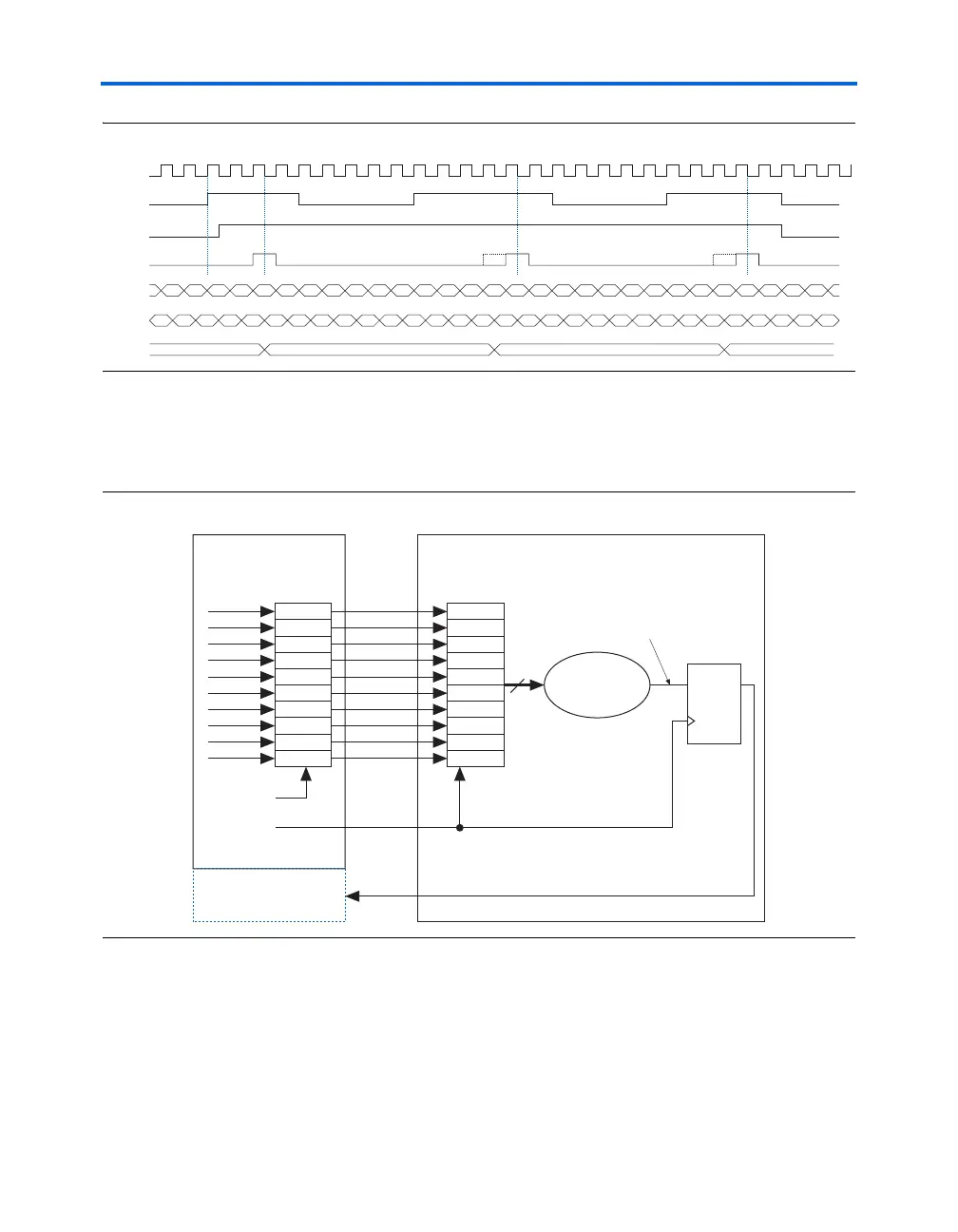

A state machine can generate the realignment signal to control the

alignment procedure. Figure 5–22 shows the connection between the

realignment signal and the rx_data_align node end.

Figure 5–22. SYNC Signal Path to Realignment Circuit

To guarantee that the rx_data_align signal generated by a user state

machine is latched correctly by the counters, the user circuit must meet

certain requirements.

■ The design must include an input synchronizing register to ensure

that data is synchronized to the ×1 clock.

10× clock

1× clock

SYNC

rxloaden

datain

receiver A

receiver B

67890123456789012345678901234

65 7890123456789012345678901234

0123456789 0123456789 1234567890 1234567890

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PD8

PD9

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PD8

PD9

Stratix Logic Array

Receiver Circuit

Parallel

Register

Register

Array

×

W/J

×

1

TXLOADEN

Hold

Register

SYNC

Realignment

Circuit

SYNC Out

10

Pattern

Detection

State Machine

Loading...

Loading...